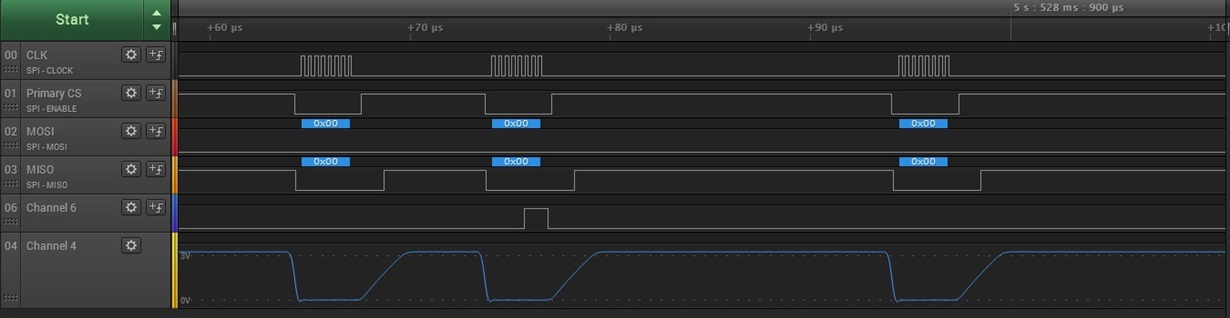

In my setup the host master device sends many SPI commands to the Tiva (especially on start-up). Irregularly, the Tiva will reply with 0x0 when it should be replying with an ack (0xA5). I have tried the following tests without correcting the issue:

1. I have scoped the MISO line when this issue occurs and have seen the line is active (pulled low) for the byte in question, but does not attempt to send an 0xA5 pattern. This rules out the condition of another device dominating the MISO line.

2. Instead of using the API call- SSIDataPut(), write directly to register: HWREG(SSI0_BASE + SSI_0_DR)

3. Hardcode an 0xA5 return (rather than variable) to rule out RAM issue

4. Added a while( SPI busy) before calling SSIDataPut()

5. Changed compiler optimization settings (default=2)

I have wiggled an led before and after the SSIDataPut() call to verify that the function is being executed at the expected time.

TM4C1290NCPDT w/ CCS 6.1

SPI is configured as:

-SSI_MODE_SLAVE

-SSI_FRF_MOTO_MODE_1

- 3.5Mhz master clock (48Mhz internal Tiva clock)

-8 data bits

Wondering if anyone has any ideas as to what I can look at?

Thanks for your input,

Jarrett