Hello,

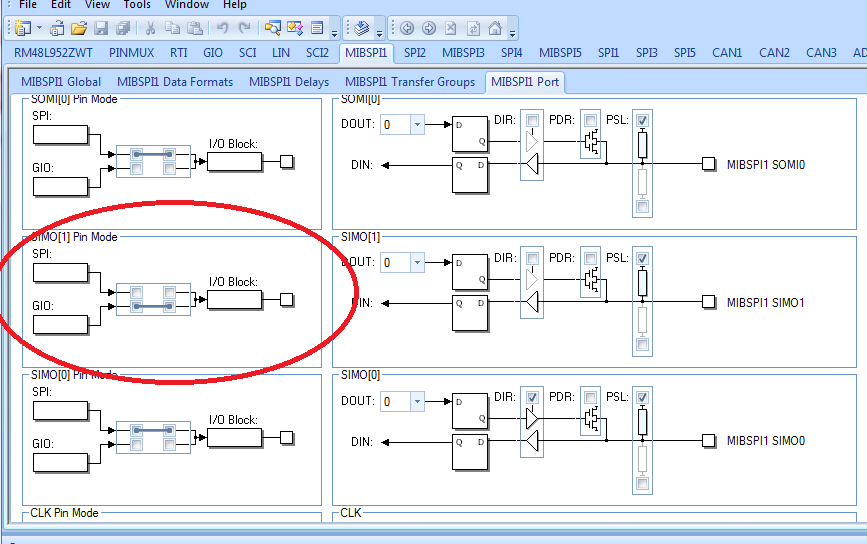

I'm using HalCoGEn 4.05.00 for RM48L952ZWT and i need to set SIMO[1] to GIO mode.

But in generated code is allways

/* SPI1 set all pins to functional */

spiREG1->PC0 = (uint32)((uint32)1U << 0U) /* SCS[0] */

| (uint32)((uint32)1U << 1U) /* SCS[1] */

| (uint32)((uint32)1U << 2U) /* SCS[2] */

| (uint32)((uint32)1U << 3U) /* SCS[3] */

| (uint32)((uint32)1U << 4U) /* SCS[4] */

| (uint32)((uint32)1U << 5U) /* SCS[5] */

| (uint32)((uint32)1U << 8U) /* ENA */

| (uint32)((uint32)1U << 9U) /* CLK */

| (uint32)((uint32)1U << 10U) /* SIMO[0] */

| (uint32)((uint32)1U << 11U) /* SOMI[0] */

| (uint32)((uint32)1U << 17U) /* SIMO[1] */

| (uint32)((uint32)1U << 25U); /* SOMI[1] */

Luděk Hezina