It's about System Design Guidelines for the TM4C129x Family

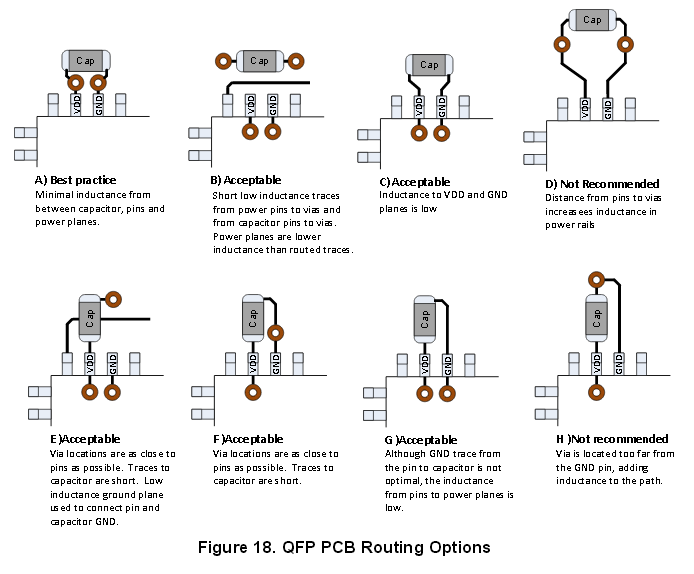

Confusing moment at page 20, Figure 18

Authors say what best practice is A (capacitor places outside trace )

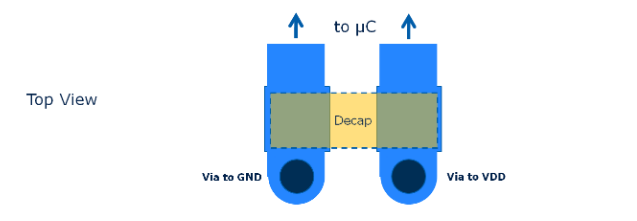

But in other literature and guides best practice is such placement when capacitor places between via to power plane and MCU pin and trace is short is possible. Example:

As I know it's a common practice.

There are the reasons for such placement (as on Picture A) in case of Tiva C?