Hi all

I am working with an SD-card and communicating using SPI (as many others do).

Everything is working fine, however I notice some delays which are slowing down the read speed.

I am reading from the SD-card by transmitting dummy bytes to toggle the SPI clock and then reading from the rx fifo.

I do something like this:

/* Fill the TX FIFO with 8 bytes to clock out the 8 receive bytes */

for( uint8_t i = 0U; i < 8U; i++ )

{

/* Put some dummy data to toggle the clock */

ROM_SSIDataPut( SDC_SSI_BASE, 0xFF );

}

/* Read back the 8 bytes in the RX FIFO */

for( bytesReceived = 0U; bytesReceived < 8U; bytesReceived++ )

{

/* Read byte (read is blocking) */

ROM_SSIDataGet( SDC_SSI_BASE, &recvData ); /* Reading from the RX fifo seems slow!!! */

pRecvData[ bytesReceived ] = (uint8_t) ( recvData & 0xFF );

}

When I monitor the SPI signals on a scope I get:

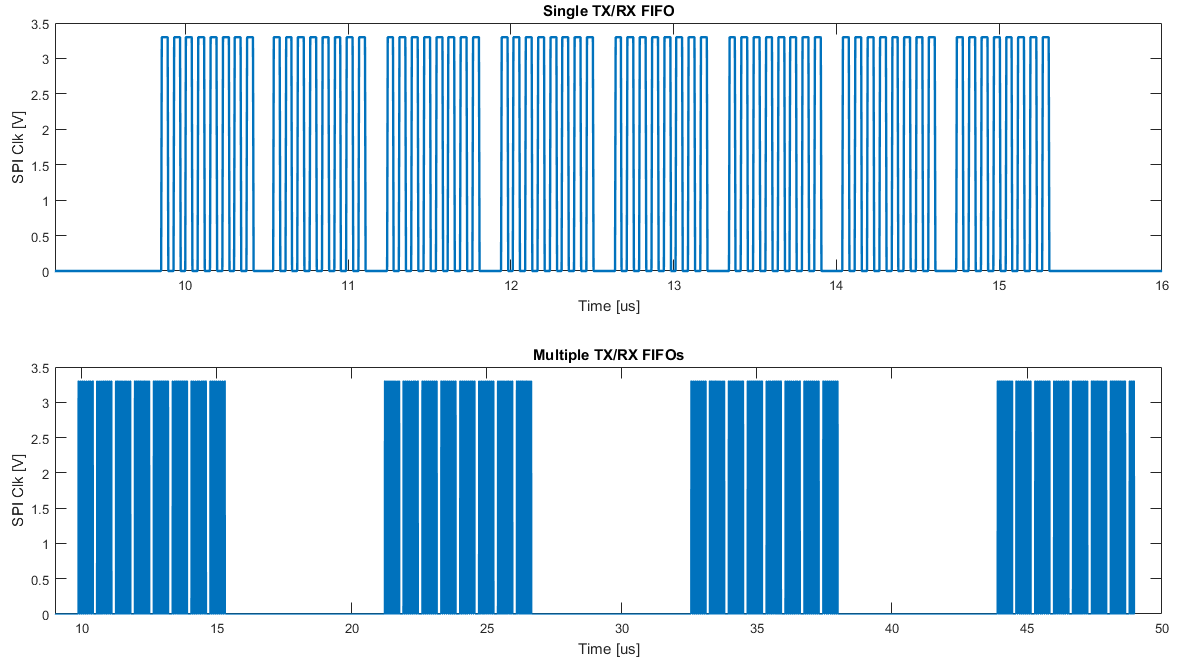

Both figures show the clock signal from the SPI line. The top plot shows a single write of 8 bytes using the 8 byte TX fifo. The bottom plot shows back to back reads (using the 8 byte tx fifo to toggle the clock and the 8 byte rx fifo to read the result).

As you see, I have a big delay between each 8 byte block. It turns out that it is the (blocking) ROM_SSIDataGet which causes the delay - when the 8 bytes are read from the rx fifo.

I wonder if there is any good reason it takes so much time to read out the bytes from the rx fifo. The data are received during the transmit (when the clock is active on the plots) - so the data should be ready when the clock toggle using tx is complete?

I know that it is most likely possible to improve this using interrupts and dma... however, for my needs, reading like this is sufficient if I can reduce the delay between the blocks.

I use a custom board, a TIVA TM4C1233D5PMI and TivaWare_C_Series-2.1.2.111

I hope it makes sense.

I appreciate any help that you can provide.

Best regards

Christian