Other Parts Discussed in Thread: TM4C1290NCPDT, TM4C1230C3PM, TM4C1292NCPDT, EK-TM4C129EXL, TM4C123GH6PM, TM4C129XNCZAD, EK-TM4C1294XL

I have a design, based on the TM4C1290NCPDT.

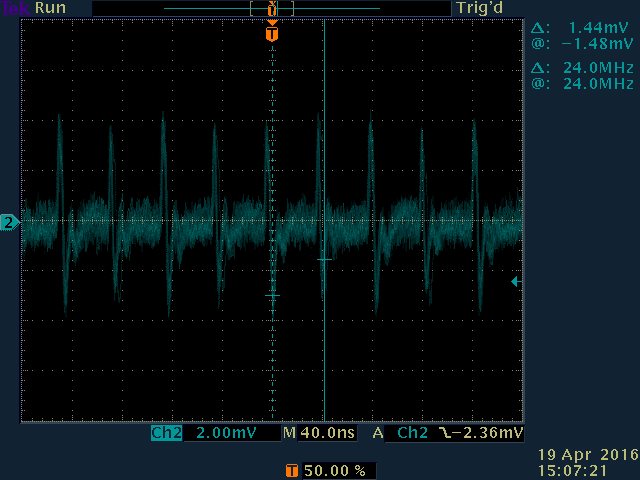

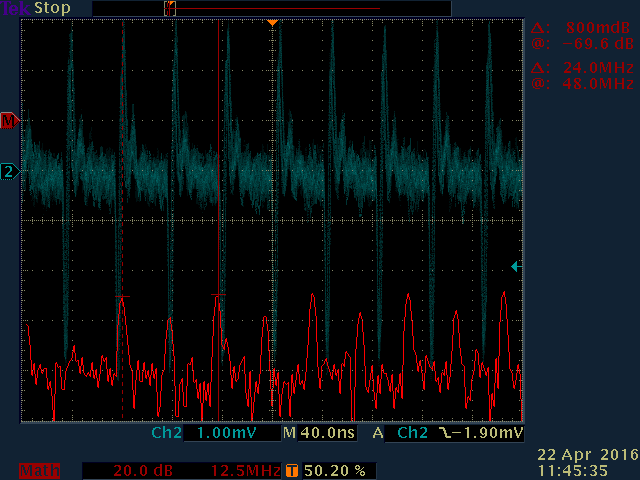

This is giving an issue when EMC testing, with an apparent 24MHz signal giving radiated emissions way above the EU thresholds, this shows particularly at 96MHz and 120MHz, although the strength of these harmonics is likely caused by the cable lengths.

Using a magnetic field probe this was traced to the TM4C, on the board.

When testing other Stellaris and TIVA micro based designs this was not apparent.

I have checked the DK-TM4C129X Tiva C Series Connected Development Kit, and this does not do this.

I have checked a TM4C1230C3PM based design, and this does not do this.

I have checked a LM3S9B92-IQC80-C5 based design, and this does not do this.

In an attempt to narrow down what may have been causing this I have performed the following 'modifications' without affecting this radiated signal:

1. Erased the flash, and cycled the power.

2. Created a new CCS project where I set the clock to use the internal oscillator, ensure that MOSC is disabled, ensure that DIVSCLK is disabled, disabled AHB for all peripherals, disabled clock gating, disabled every peripheral, powered off every peripheral and disabled the PLL.

int main(void)

{

/* Do a setup to disable everything. This should show if the 24MHz */

/* giving issue with radiated emissions is endemic to this part... */

/* Setup the CPU clock, to use int 16MHz */

SysCtlClockFreqSet((SYSCTL_OSC_INT | SYSCTL_USE_OSC | SYSCTL_CFG_VCO_320), 16000000);

SysCtlMOSCConfigSet(SYSCTL_MOSC_NO_XTAL | SYSCTL_MOSC_PWR_DIS);

/* Disable the DIVSCLK output (should be all defaults) */

SysCtlClockOutConfig((SYSCTL_CLKOUT_DIS | SYSCTL_CLKOUT_SYSCLK), 1);

/* Disable ALL peripherals. */

SysCtlGPIOAHBDisable(SYSCTL_PERIPH_GPIOA);

SysCtlGPIOAHBDisable(SYSCTL_PERIPH_GPIOB);

SysCtlGPIOAHBDisable(SYSCTL_PERIPH_GPIOC);

SysCtlGPIOAHBDisable(SYSCTL_PERIPH_GPIOD);

SysCtlGPIOAHBDisable(SYSCTL_PERIPH_GPIOE);

SysCtlGPIOAHBDisable(SYSCTL_PERIPH_GPIOF);

SysCtlGPIOAHBDisable(SYSCTL_PERIPH_GPIOG);

SysCtlGPIOAHBDisable(SYSCTL_PERIPH_GPIOH);

SysCtlGPIOAHBDisable(SYSCTL_PERIPH_GPIOJ);

SysCtlPeripheralClockGating(false);

SysCtlPeripheralDisable(SYSCTL_PERIPH_ADC0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_ADC1);

SysCtlPeripheralDisable(SYSCTL_PERIPH_CAN0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_CAN1);

SysCtlPeripheralDisable(SYSCTL_PERIPH_CCM0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_COMP0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_EEPROM0);

// SysCtlPeripheralDisable(SYSCTL_PERIPH_EMAC); // not on TM4C1290

// SysCtlPeripheralDisable(SYSCTL_PERIPH_EPHY); // not on TM4C1290

SysCtlPeripheralDisable(SYSCTL_PERIPH_EPI0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOA);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOB);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOD);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOE);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOF);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOG);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOH);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOJ);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOK);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOL);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOM);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPION);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOP);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOQ);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOR);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOS);

SysCtlPeripheralDisable(SYSCTL_PERIPH_GPIOT);

SysCtlPeripheralDisable(SYSCTL_PERIPH_HIBERNATE);

SysCtlPeripheralDisable(SYSCTL_PERIPH_I2C0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_I2C1);

SysCtlPeripheralDisable(SYSCTL_PERIPH_I2C2);

SysCtlPeripheralDisable(SYSCTL_PERIPH_I2C3);

SysCtlPeripheralDisable(SYSCTL_PERIPH_I2C4);

SysCtlPeripheralDisable(SYSCTL_PERIPH_I2C5);

SysCtlPeripheralDisable(SYSCTL_PERIPH_I2C6);

SysCtlPeripheralDisable(SYSCTL_PERIPH_I2C7);

SysCtlPeripheralDisable(SYSCTL_PERIPH_I2C8);

SysCtlPeripheralDisable(SYSCTL_PERIPH_I2C9);

SysCtlPeripheralDisable(SYSCTL_PERIPH_LCD0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_ONEWIRE0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_PWM0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_PWM1);

SysCtlPeripheralDisable(SYSCTL_PERIPH_QEI0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_QEI1);

SysCtlPeripheralDisable(SYSCTL_PERIPH_SSI0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_SSI1);

SysCtlPeripheralDisable(SYSCTL_PERIPH_SSI2);

SysCtlPeripheralDisable(SYSCTL_PERIPH_SSI3);

SysCtlPeripheralDisable(SYSCTL_PERIPH_TIMER0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_TIMER1);

SysCtlPeripheralDisable(SYSCTL_PERIPH_TIMER2);

SysCtlPeripheralDisable(SYSCTL_PERIPH_TIMER3);

SysCtlPeripheralDisable(SYSCTL_PERIPH_TIMER4);

SysCtlPeripheralDisable(SYSCTL_PERIPH_TIMER5);

SysCtlPeripheralDisable(SYSCTL_PERIPH_TIMER6);

SysCtlPeripheralDisable(SYSCTL_PERIPH_TIMER7);

SysCtlPeripheralDisable(SYSCTL_PERIPH_UART0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_UART1);

SysCtlPeripheralDisable(SYSCTL_PERIPH_UART2);

SysCtlPeripheralDisable(SYSCTL_PERIPH_UART3);

SysCtlPeripheralDisable(SYSCTL_PERIPH_UART4);

SysCtlPeripheralDisable(SYSCTL_PERIPH_UART5);

SysCtlPeripheralDisable(SYSCTL_PERIPH_UART6);

SysCtlPeripheralDisable(SYSCTL_PERIPH_UART7);

SysCtlPeripheralDisable(SYSCTL_PERIPH_UDMA);

SysCtlPeripheralDisable(SYSCTL_PERIPH_USB0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_WDOG0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_WDOG1);

SysCtlPeripheralDisable(SYSCTL_PERIPH_WTIMER0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_WTIMER1);

SysCtlPeripheralDisable(SYSCTL_PERIPH_WTIMER2);

SysCtlPeripheralDisable(SYSCTL_PERIPH_WTIMER3);

SysCtlPeripheralDisable(SYSCTL_PERIPH_WTIMER4);

SysCtlPeripheralDisable(SYSCTL_PERIPH_WTIMER5);

SysCtlPeripheralPowerOff(SYSCTL_PERIPH_CAN0);

SysCtlPeripheralPowerOff(SYSCTL_PERIPH_CAN1);

// SysCtlPeripheralPowerOff(SYSCTL_PERIPH_EMAC); // not on TM4C1290

// SysCtlPeripheralPowerOff(SYSCTL_PERIPH_EPHY); // not on TM4C1290

SysCtlPeripheralPowerOff(SYSCTL_PERIPH_LCD0);

SysCtlPeripheralPowerOff(SYSCTL_PERIPH_USB0);

SysCtlUSBPLLDisable();

/* Now do an infinite loop */

while (1) {}

}

3. Physically cut the pins to all pins for PortA, B, C, D, E, F, G, H, J, K, L, M, N, P and Q. Essentially all of the I/O pins. This is listed as acceptable for unused I/O.

4. Disconnected the hibernation pins, VBAT, HIB, WAKE, XOSC0 and XOSC1. This is listed as acceptable for these pins when unused.

5. disconnected the MOSC pins OSC0 and OSC1. This is listed as acceptable for these pins when unused.

So I now have the TM4C1290NCPDT connected to just the power pins, including VREFA+ and VDDA, with a 100k pull-up on RST, and this still has the unintended 24MHz radiated emissions.

If I hold the TM4C1290NCPDT in reset, by connecting ONLY the RST input to Ground, then the 24MHz radiated emissions stops, verifying that the TM4C is the source.

Is this a known issue for this particular part? I have not found anything to this end in the errata document SPMZ850D.

Is this an issue with just the TM4C1290?

Is this an issue with TM4C in the PDT package?

Thanks in advance for any help,

Kevin.