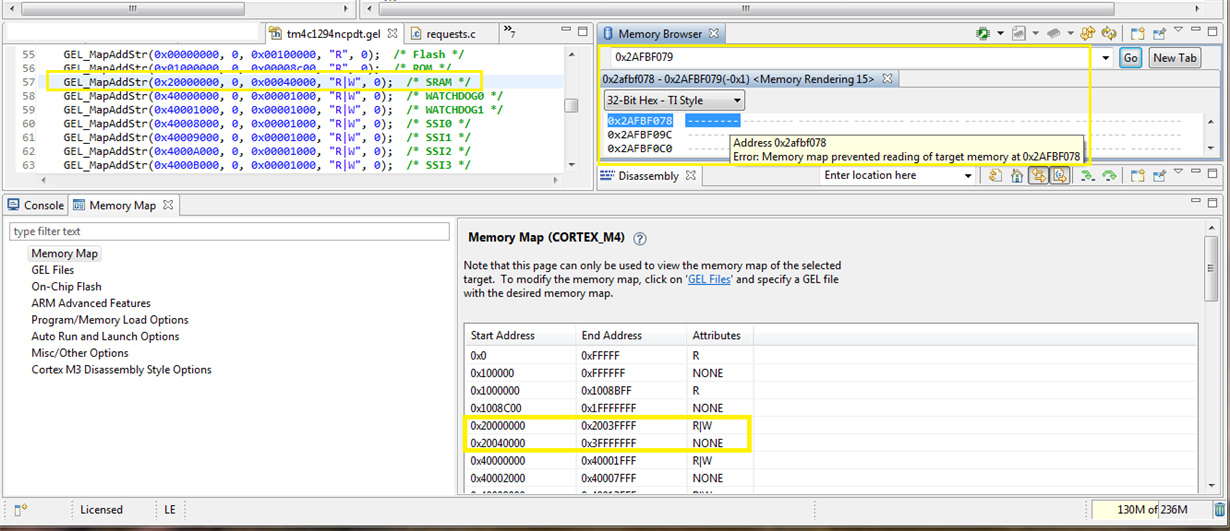

TM4c1294ncpdt Gel file shows the SRAM range as per memory map in datasheet. Notice the R/W attribute is NONE for the second part of SRAM range. Consequently this is the same precise memory location (0x2AFBF079) that persistently coincides with random bus fault 11 status. Have changed the project compiler to 5.14 and set optimization in the middle to see if that helps. Also getting same Memory Browser error if the target is running or paused.

See what I mean and thanks for looking under the hood!