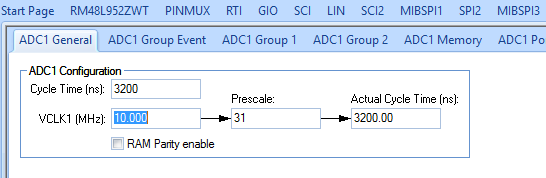

Am I correct that in order to accomplish the following ADC clock timing request?

1.6.2. Configure the ADCLK frequency to VCLK/32 by writing 0x0000001F to the clock divider into the Clock Control Register (ADCLOCKCR at 0xFFF7C008). Note that VCLK was previously set to the oscillator frequency (20MHz) divide by 2, or 10Mhz.

that I have to set the Cycle Time in the ADC1 Configuration to 3200 ns.

Here is my thinking. VCLK1 timing is 10 MHz. The request is to make that VCLK/32 or 0.3125 MHz, which I converted to 0.0000032 seconds. Multiplying by 1000*1000*1000, gets me 3200 ns, hence the entry above.

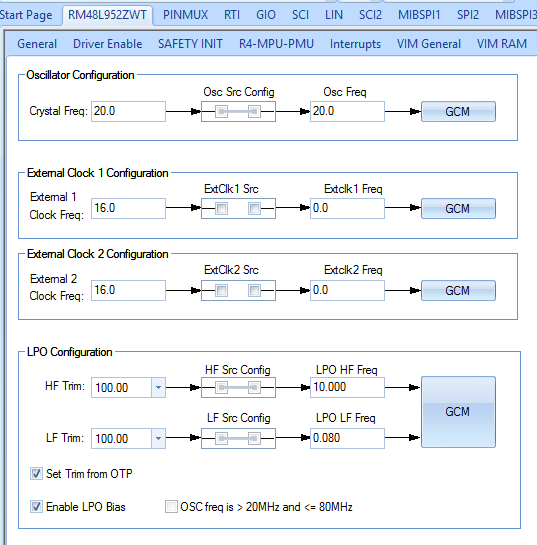

I already changed the clock speed to 20 MHz from the default 16 MHz, as shown here in the Clk Source tab.