Other Parts Discussed in Thread: TMS570LC4357, TMS570LS3137

Thank you Anthony for the explanation.

In STC, what is the MISR value mean (mentioned in STC module as "reflected in registers CPUx_CURMISR[3:0] " ) ?

Same as STC I have few queries on PBIST in TMS570LC4357

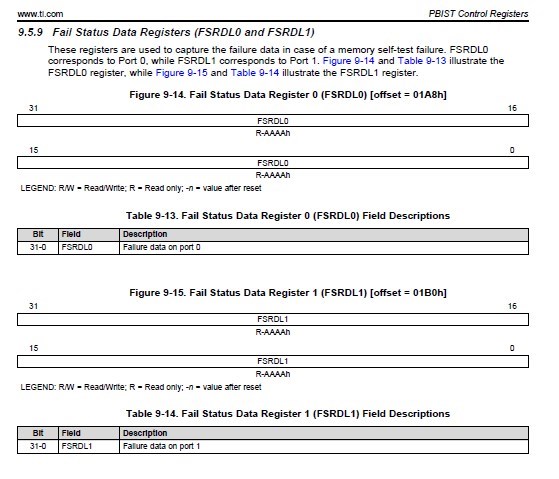

1) What is Port 0 / Port 1 mentioned in PBIST?

2) What exactly this Failure Data on Port(0/1) indicate? How is this status useful after PBIST test?

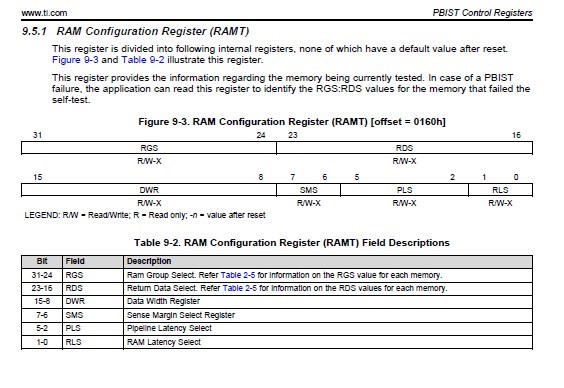

3) In this register can you please explain the fields DWR,SMS,PLS and RLS and their use in this test?

4) On occurrence of a PBIST failure, will the RGS:RDS indicate the current failure that occurred or for the First Failure (since Failure Address Status Register shows the address of the failure that occurred first)?