Seems as if the example program (deadband.c) inserts delay asserting a single dead band generator (DBG) and fails to produce same results when 2 or more DBG and periods are configured.

Invoking DBG delay without quickly clearing DB delay each cycle Fails if synchronous updates are enabled?

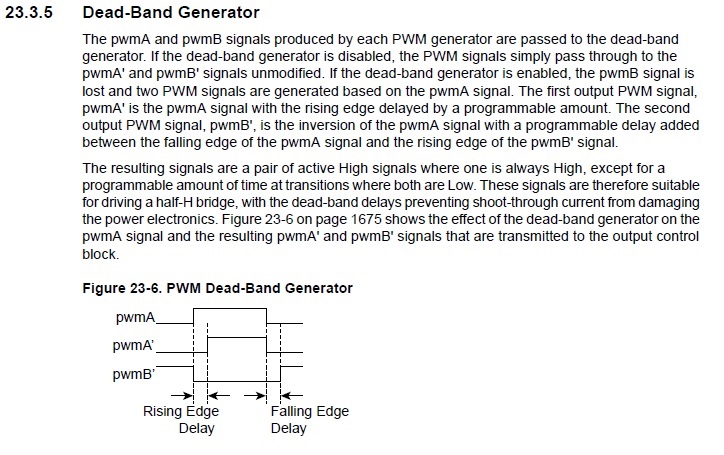

TM4C1294NCPDTi3 data sheet fails to mention the PWM generator outputs are coupled as programmer believes they are, check below text. Might that be giving others a false reality of phase pair co-partner 1/2 bridge signals? Seems perpetual enabled DBG's (per example) actually produce useless bridge wave forms. There seems to be a Full DB mode 6 and a partially enabled DB mode since PWMbnDBFALL asserts even after PWMnDBCTRL bit has been cleared.

Started to do a rewrite (deadband.c) for EK-TM4C294; Discovered DBG's are not being cleared after each pin write cycle and (Gen_Mode_NoSync) has been enabled.