Hi TI Experts,

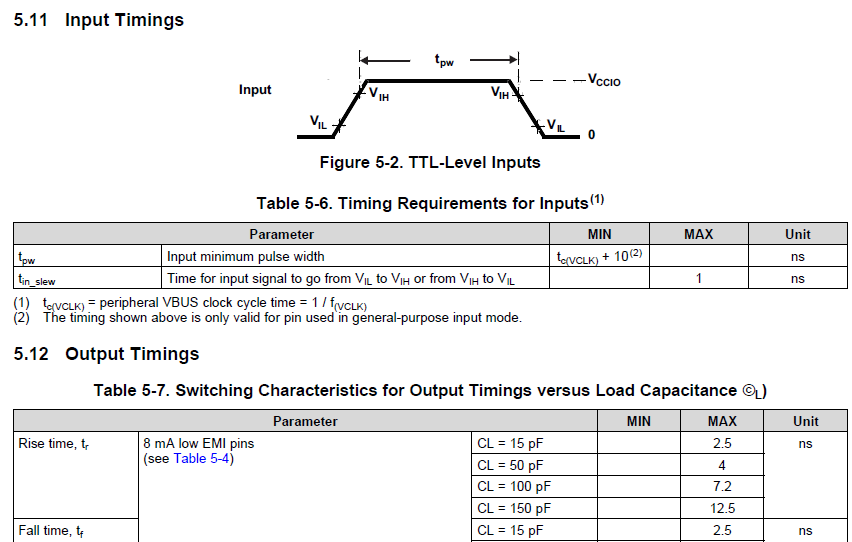

I found in TMS570LS1114 datasheet described as follows

Does this MCU need tin_slew "Time for input signal to go from VIL to VIH or from VIH to VIL" on every input pin to be less than 1ns to work properly?

I think this requirement is kind of too strict. On the other hand, we can see the output timings of this MCU, depending on load capacitance, the maximum Tr or Tf can be as high as 12.5ns, or 2.5ns for Cl = 15pF.

A 2.5ns input slew time will not cause most IC to work abnormally. So why Hercules MCU define a 1ns maximum input slew time?