Hi,

Hi, I'm running code on Cortex TM4C129ENCPDT.

Our boot loader runs and make a jump to address 0x8000 where our application resides.

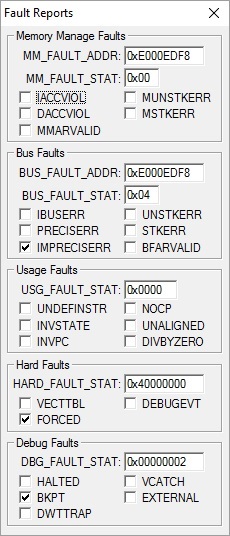

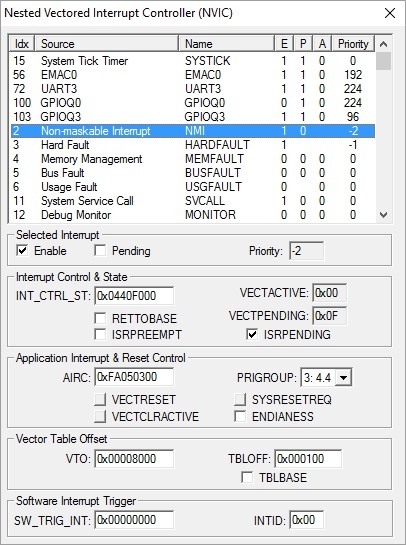

our application/main.c runs until I enable interrupts (call to IntMasterEnable() ) and immediately after, I jump to hard fault handler.

If I disable our boot loader/Ethernet configuration, our application runs fine. This is telling me that there is no problem with the Ethernet interrupts that are waiting to be serviced.

I tried disabling all interrupts and clearing pending interrupts after the jump to 0x8000 in our application/main( ) but no success:

- SysCtlPeripheralReset( ) for all peripherals

- IntDisable( ) for all interrupts

- IntPendClear( ) for all interrupts

I have included extract of the boot loader main( ) and the application main( ).

//extract of our main.c

int main(void) {

IntMasterDisable();

SystemInit(); //clock and system setup

GPIO_Init(); //setup GPIO

IntMasterEnable(); //goes into hard fault AFTER this instruction

os_sys_init(taskInit);

}

//extract of our bootloader

int main.c(void) {

IntMasterDisable( );

SystemInit(); //set's gSysCtlClock

GPIO_Init();

EnetReconfig(gSysCtlClock); //from boot_loader/bl_emac.c

//bootloader code goes here ...

HWREG(NVIC_VTABLE) = 0x8000;

jump_to_application();

}

//jump to application

__asm void jump_to_application(void) {

ldr r1, [r0]

mov sp, r1

ldr r0, [r0, #4]

bx r0

}

What Am I missing?

Khaled.