Hi,

A customer reported issues with the EMAC module on RM57. They like to upgrade their current system from RM48 to RM57 for this they simply produced new boards with RM57 on them instead. Now they started to see that they lose some packets, they reported a packet loss of 5-50% depending on the board with identical SW. The Ethernet driver is the same between RM48 and RM57.

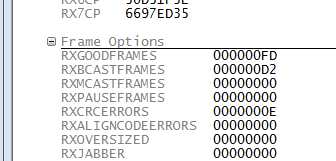

The packet statistics showed that the amount of lost packets equals the amount of CRC errors:

So the questions are:

- Are there any differences between RM48 and RM57 that could cause this issue?

- When does the EMAC performs the CRC check before, or after the frame was copied into the RAM?

- How is the EMAC clocked for receiving frames is the 50MHz clock generated by the MCU or the PHY (DP83848, RMII)?

Any other ideas what could go wrong in this setup?

Thanks,

Christian