Other Parts Discussed in Thread: LM3S8971, TM4C1294NCPDT

MCU = TM4C1294NCPDTi3

Conditions: (3 Phase PWM motor drive)

1. PWM GEN mode up/down count, Gen mode Sync, Gen mode Sync global and or Gen mode DB sync global or local.

2. PWM GEN0 Raw interrupt load count zero for processing GEN sync updates, 3 time base synched PWM generators.

3. PWMnDBRISE/FALL register values = 1,2,3,4,5, 6 etc...

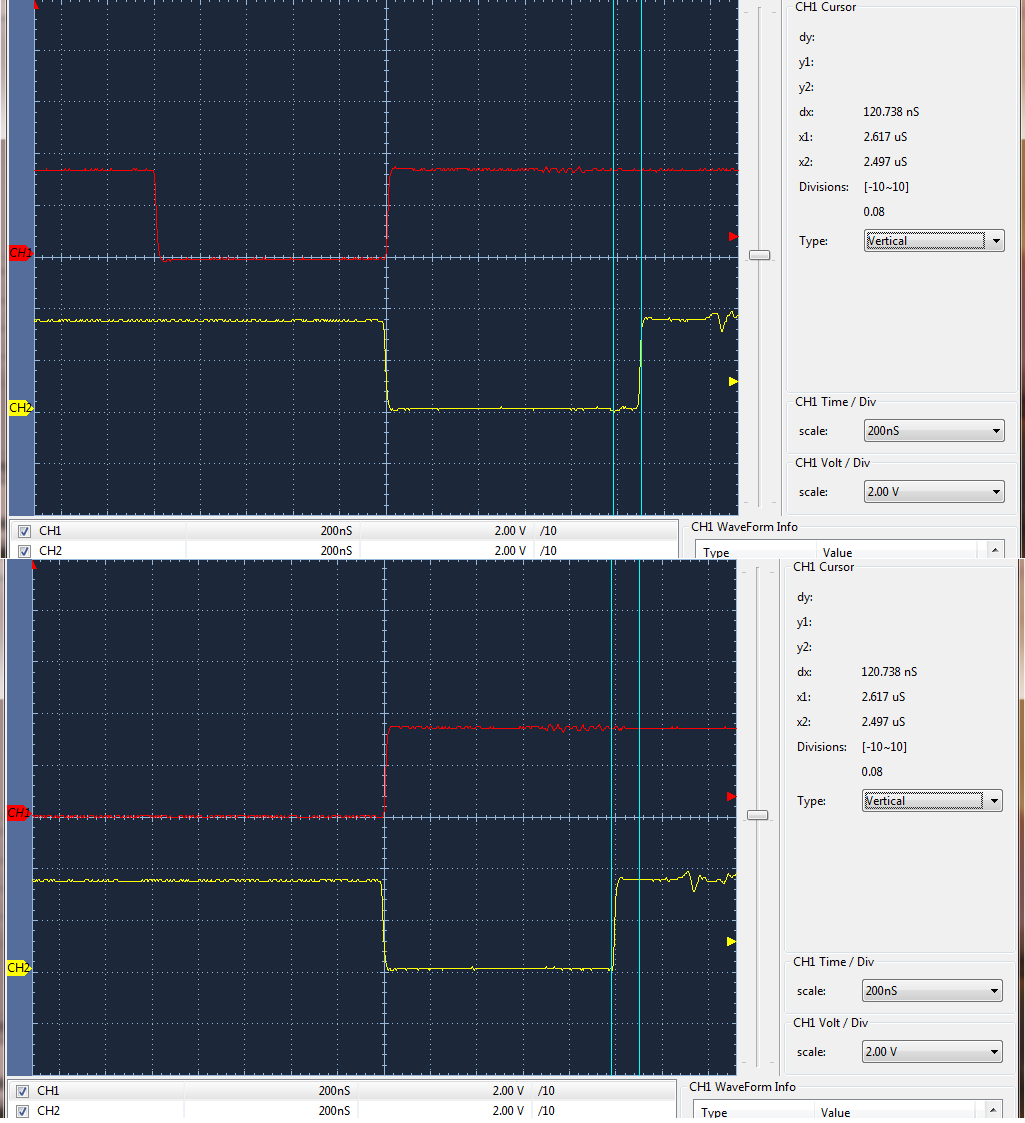

A. If ever PWMnCMPA/B register values are set extremely low say (1-42) an immediate dead lock occurs in new values (above) the previous value set in PWMnCMPB furthermore being ignored and or counted during synchronous updates. That results in the pulse width of PWM0 pwmB not being constrained in monotonic counts matching the compare values of PWMnCMPB, suspecting only during (down) counts. That results in numerous missing edge times in the down counts of would be matches CMPB that remain ignored.

B. if ever PWMnCMPA/B values are initially set higher say 600 the same basic condition CMPB described above occurs during synchronous updates. However only up to the value previously loaded seemingly while counting down and loading any higher values CMPB are ignored by the PWM generator. Thus results in missing edge times pwmB and the wave form produced in the bridge is missing artifacts.

Provided register monitors recording differences CMPB in two different load values and resulting wave form (captures). That is the only way to detect the load count value failure since CCS debug shows CMPA/B register values being equal during the synchronous updates. The outcome of ignoring matches CMPB are missing edges in the pulse width changes made during synchronous update.

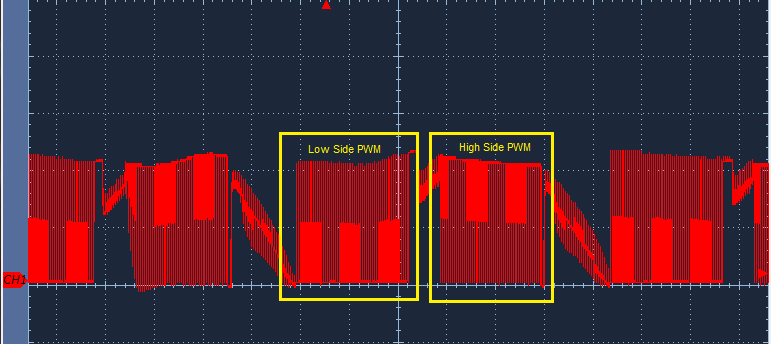

Newly discovered below scope capture Trapezoidal wave forms (produce) low side PWM when CMPB is not being (completely) ignored. Fast decay then produces in Full Bridge low side PWM when setting a starting pulse width CMPB below 100% duty cycle. That Is an indication CMPB becomes (jammed) when set nearly 100% duty and refuses to then process rising duty cycle values during synchronous updates of all 3 PWM generators.

Why are CMPB down count changes being ignored in synchronous updates after 100% duty cycle is set in all 3 generators?

Notice low side PWM now works when Stellaris (team engineers) failed, releasing SW public domain (claiming) low side PWM in RDK user manual! That falsified claim (low side PWM fast decay mode) mislead all growing engineers down a black hole of singularity.