TM4C1294NCPDTi3

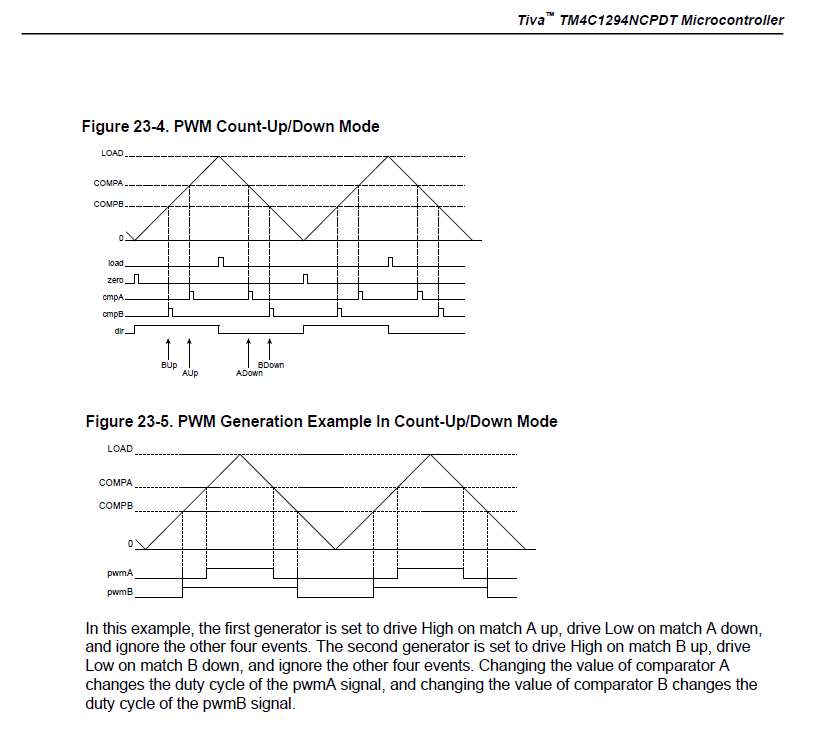

Is it possible if the PWM modules generators duty cycles or pulse width (if different values) are not staggered in descending monotonic order (Fig 23-5) PWMnCMPB might ignore synchronous updates of this register?

Notice datasheet 23-5 suggest center aligned overlapping signals and illustrates CMPB has roughly 20% more duty cycle than CMPA.

What happens if CMPB match value is higher than CMPA match value and how does that monotonic reversal affect dead band generators performance?