Hello,

I am attempting to bring up a custom board which has one TM4C1294NCPDT and one TM4C123GH6PM. I am attempting to program these devices using the 'debug out' feature of the TM4C1294 launchpad. Attempting to program either device results in a "CORTEX_M4_0: Error connecting to the target" message.

To keep things simple, I am focusing on the TM4C123 device for now. Here is what I checked so far:

- VDD is at 3.3V, with about 100-200mV ripple observed at decoupling caps. All VDD pins are connected.

- VDDC is at 1.2V, with about 100-200mV ripple observed at decoupling caps. This net is not shared with any other devices. All VDDC pins are connected.

- All GND pins are connected.

- RESETn is pulled up to 3.3V with a 10K resistor.

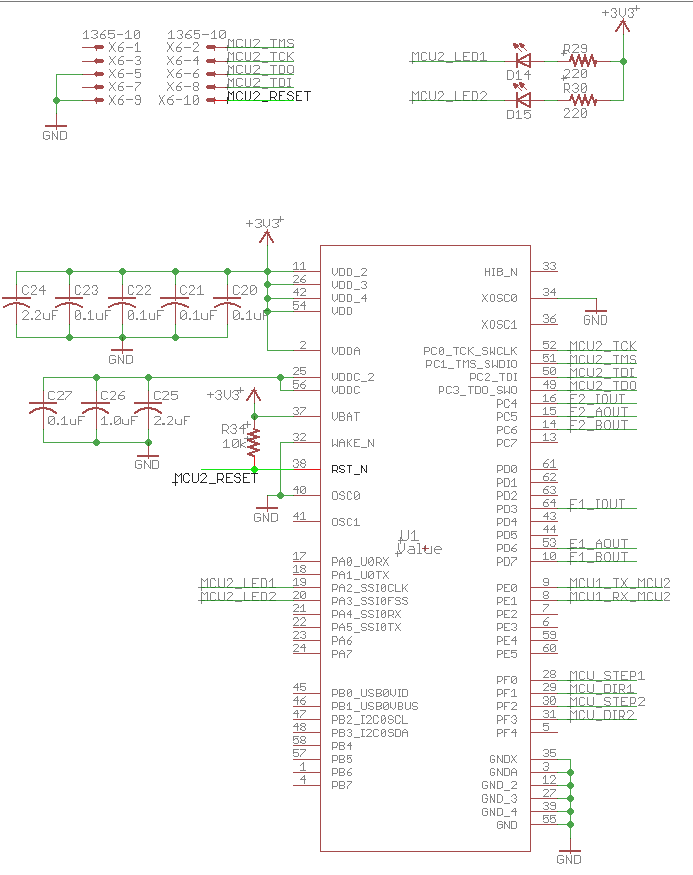

- Continuity check between the following JTAG signals on target board and X1 header on the Launchpad showed a good connection: TMS, TCK, TDO, TDI, RESET, GND.

- All resistors were removed from the X1 header on the Launchpad; R40 was removed as well.

- Brief activity is observed on TMS, TCK, TDO, TDI on the target side when attempting to program the device.

Here is what the activity on TDO looks like. Except for the first burst of activity, all subsequent bursts have the pattern seen in bursts 2 and 3. This continues for about 30 milliseconds.

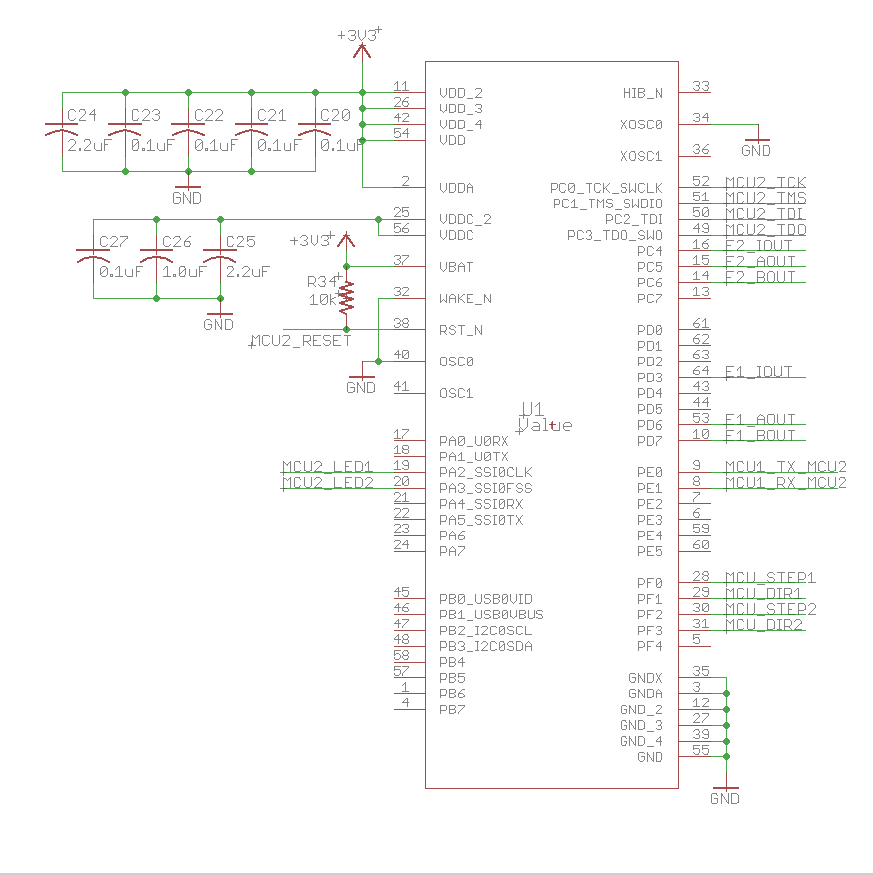

This is how the TM4C123 hardware is set up. My intention is to run the device from PIOSC.

I am using CCSv6.1.3.00033. I haven't had any problems programming TM4C chips on launchpads before, but this is the first time trying to use the 'debug out' feature.

Any suggestions on what I should investigate next?

Thanks