Other Parts Discussed in Thread: TM4C129ENCPDT, EK-TM4C129EXL, AM3352

Hi,

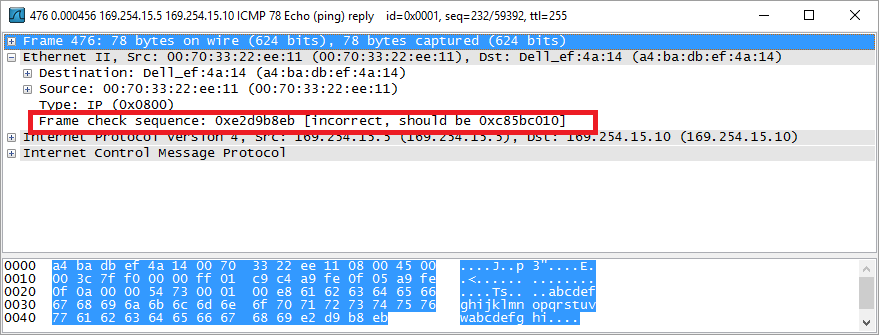

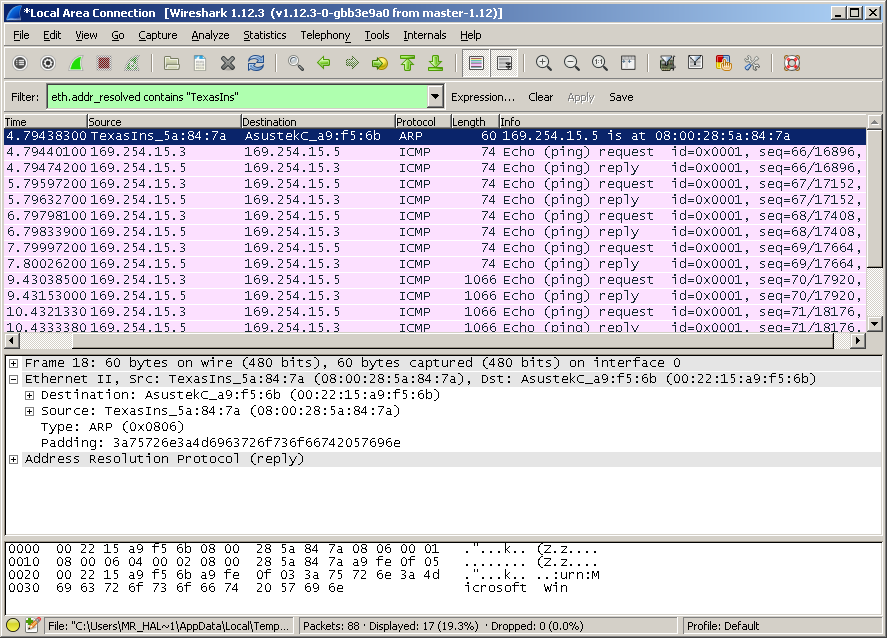

I have the Ethernet port working (Tx and Rx). All frames are correct except for the ping reply message where wireshark is reporting a Crc error.

// Configure for use with the internal PHY.

EMACPHYConfigSet( EMAC0_BASE,

EMAC_PHY_TYPE_INTERNAL |

EMAC_PHY_INT_MDIX_EN |

EMAC_PHY_AN_100B_T_FULL_DUPLEX);

// Initialize the MAC and set the DMA mode.

EMACReset(EMAC0_BASE); // Reset the MAC.

EMACInit(EMAC0_BASE,gSysCtlClock,

EMAC_BCONFIG_MIXED_BURST |

EMAC_BCONFIG_PRIORITY_FIXED,

4,

4,

0);

EMACConfigSet(EMAC0_BASE,

( EMAC_CONFIG_FULL_DUPLEX | //operate in full- or half-duplex mode

EMAC_CONFIG_CHECKSUM_OFFLOAD | //enables header checksum checking

EMAC_CONFIG_7BYTE_PREAMBLE | //number of bytes of preamble added

//to the beginning of every transmitted

//frame

EMAC_CONFIG_IF_GAP_96BITS | //interframe gap between transmitted

//frames

EMAC_CONFIG_USE_MACADDR0 | //which MAC address is used during

//insertion or replacement for all

//transmitted frames

EMAC_CONFIG_SA_FROM_DESCRIPTOR | //Control over insertion or replacement

//of the source address in all

//transmitted frames

EMAC_CONFIG_BO_LIMIT_1024 ), //The back-off limit determines the

//range of the random time that the MAC

//delays after a collision and before

//attempting to retransmit a frame.

( EMAC_MODE_RX_STORE_FORWARD | //receive DMA to read frames from

//the FIFO only after the complete

//frame has been written to it.

//If this mode is enabled, the

//receive threshold is ignored.

EMAC_MODE_TX_STORE_FORWARD | //start transmitting a frame only

//after the whole frame has been

//written to the transmit FIFO.

//If this mode is enabled, the

//transmit threshold is ignored.

EMAC_MODE_TX_THRESHOLD_64_BYTES | //transmit FIFO threshold

EMAC_MODE_RX_THRESHOLD_64_BYTES ), //receive FIFO threshold

0);

for(ui32Loop = 0; ui32Loop < NUM_TX_DESCRIPTORS; ui32Loop++)

{

//DES0

//control and status bits

//Bit 31 is the ``OWN'' bit which, when set, indicates

//that the hardware has control of the descriptor.

g_psTxDescriptor[ui32Loop].ui32CtrlStatus =(

DES0_TX_CTRL_LAST_SEG |

DES0_TX_CTRL_FIRST_SEG |

DES0_TX_CTRL_INTERRUPT | //send interrupt on completion

DES0_TX_CTRL_CHAINED); //DES3 contains next descriptor address

// DES0_TX_CTRL_IP_ALL_CKHSUMS);//insert CRC

// DES0_TX_CTRL_REPLACE_CRC); //updated and replace CRC

// DES0_TX_CTRL_NO_CHKSUM); //don't insert CRC

//DES1

//size of the buffer attached to the descriptor and various control bits

g_psTxDescriptor[ui32Loop].ui32Count = (

DES1_TX_CTRL_SADDR_NONE |

(TX_BUFFER_SIZE << DES1_TX_CTRL_BUFF1_SIZE_S));

//DES2

//pointer to the buffer containing the data to transmit

g_psTxDescriptor[ui32Loop].pvBuffer1 = g_pui8TxBuffer;

//DES3

//set the next descriptor address

g_psTxDescriptor[ui32Loop].DES3.pLink =

(ui32Loop == (NUM_TX_DESCRIPTORS - 1)) ?

g_psTxDescriptor : &g_psTxDescriptor[ui32Loop + 1];

}

Can anyone tell me what could be the problem?

Khaled.