Hi,

I want to confirm if my understanding about lockstep is correct.

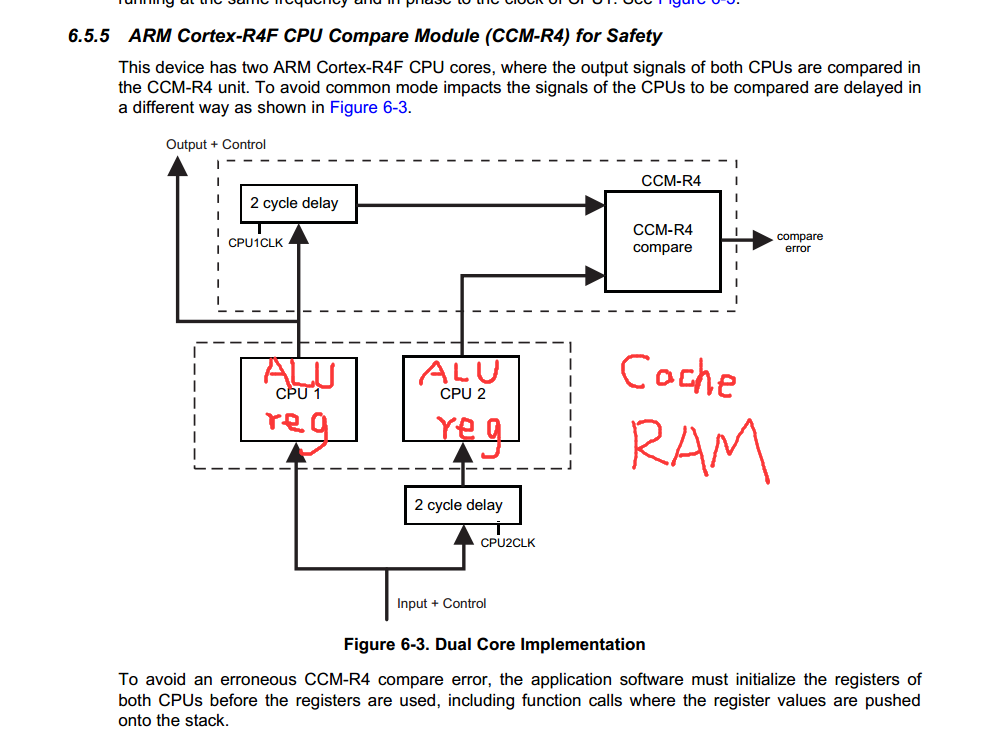

see the following screenshot.

There are two sets of registers in each core? what about the ALU, Decode, components, also each core has a seperate one?

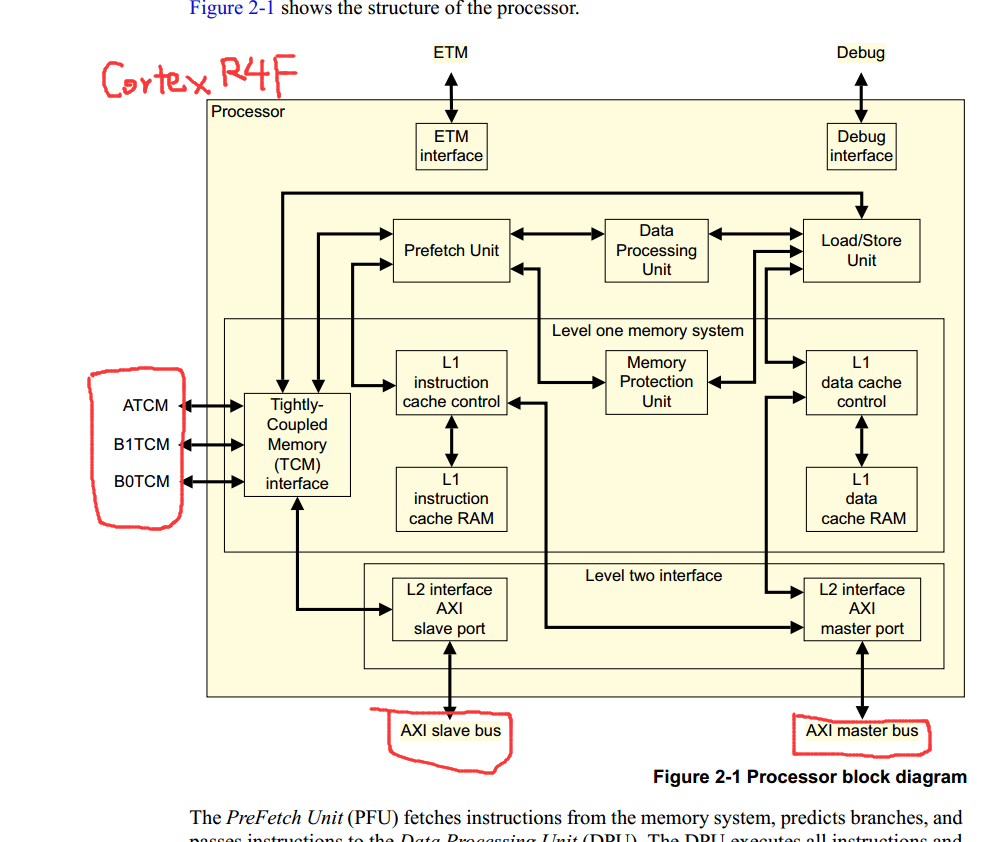

what about the cache and RAM? do they share the same one cache?

I also don't understand the "the CPU pushed the internal registers on to the stack on a function call, which could lead to the detection of the core comparision error", why this happens?