Other Parts Discussed in Thread: TM4C129ENCPDT

Using TM4C129ENCPDT and Kiel uvision 5.15.0

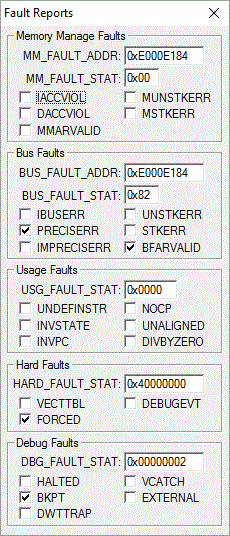

I'm trying to disable interrupt #66 (call to tivaware/interrupt.c/IntDisable(INT_EPI0)) from withing a task, but I keep getting a hard fault.

If I execute the same code from withing main, the code runs to completion.

Any ideas?

Khaled.