Other Parts Discussed in Thread: HALCOGEN

Hello TI,

Development board: TMDX470MF066HDK Hercules Development Kit

I am using HET to generate a PWM signal. The driver level code of HET is generated from HALCoGen.

My application demands the PWM pin to be LOW when needed. I am just changing duty cycle to 0 % for the same.

When i change duty cycle from 100 % to 0 %, the HET pin still persists to be HIGH. However any changes from 1-99 % duty cycle to 0% is working absolutely fine, the HET pin becomes LOW.

The issue gets resolved with the following work-arounds, but I still don't understand what's going wrong!

Workaround 1: When I put a delay after PwmSetDuty(0), the pin becomes LOW(0 % duty cycle) from HIGH(100 % duty cycle)

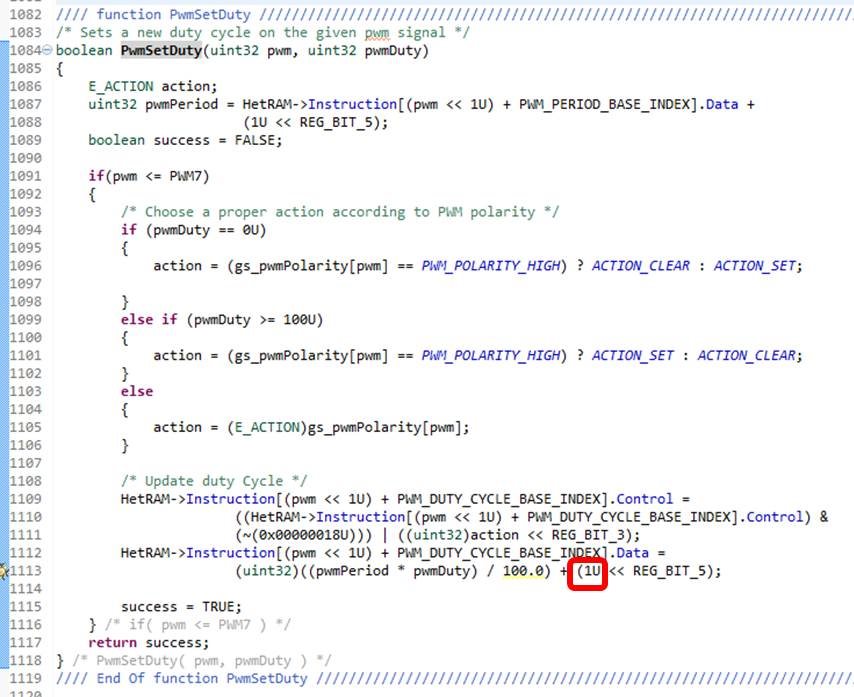

Workaround 2: This is how my PwmSetDuty Function looks like:-

When I increment the count of DATA field in PWCNT instruction by 1, that is replacing 1U (marked red in image) with 2U.

However this will intoduce inaccuracy in the generated pulses, which is undesirable.

The HET pin becomes LOW(0 % duty cycle) from HIGH(100 % duty cycle) after this work-around.

Please help me in finding the cause of issue and resolving the same.

If I have created any confusion please get back to me.

Thanks in advace!