Tool/software: Code Composer Studio

Hi,

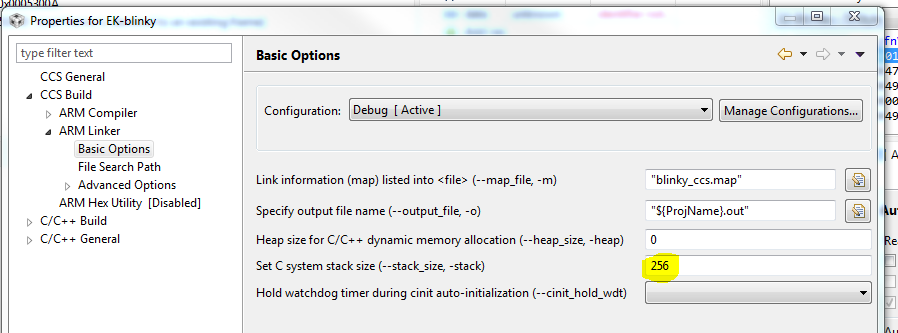

I had hard times finding out that the stack is by default 128 words only, is not 8 byte aligned and not located at RAMTOP at all. Is there any reason why you TI guys choose that strange layout?

From my understanding the stack:

- should be reasonable large (not 128 words). Maybe 1/4 of the total RAM would be a good start

- should be on a 8 byte boundary (it's written somewhere in the ARM ABI spec, if its not 8 byte aligned it breaks floating point stuff in the C library, found out the hard way)

- should not be inside the BSS in the middle of my variables but at RAMTOP (stack grows downwards from my understanding). It leads to the funny effect that depending on how many variables by chance end up in front of the stack, the alignment shifts, breaking the 8 byte alignment rule and floating point works or works not on a random base (also found out the hard way)

- should be initialized properly using the sections defined in the in the linker script (from what i see now the script is totally ignore and the stack pointer points into pui32Stack which is a variable in BSS

- I'm not sure if we actually create two stacks this way, not knowing where the libc actually expect the stack. I assume libc uses the references from the linker script but we setup the stack elsewhere

Can someone explain me why it is implemented in this way? I've never seen it on any other ARM platform (ST, NXP). And I still have mysterious crashes I blame on the weird stack management.

I changed the startup code to "static uint32_t __attribute__((aligned(0x8))) pui32Stack[32768];" to address the issues above but still crashes.

Markus