Tool/software: TI-RTOS

This is our .cfg configuration.

var HeapMem = xdc.useModule('ti.sysbios.heaps.HeapMem');

var heapMemParams = new HeapMem.Params();

heapMemParams.size = 0x100000;

heapMemParams.sectionName = ".external";

heapMemParams.buf = 0x60000000;

heapMemParams.instance.name = "sdram";

Program.global.sdram = HeapMem.create(heapMemParams);

Memory.defaultHeapInstance = Program.global.sdram; <.------------------------- LINE X

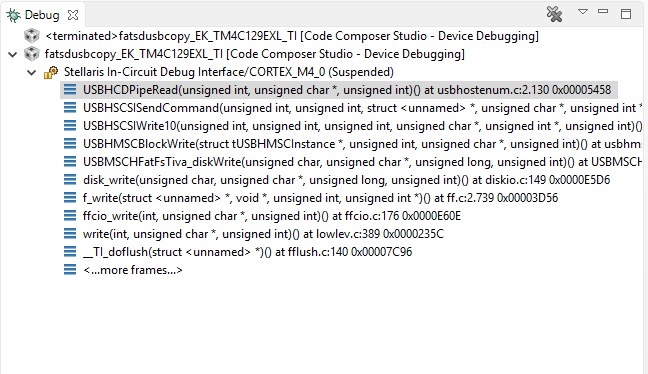

When this line X is enabled f_write() function locks at USBHCDPipeRead(uint32_t ui32Pipe, uint8_t *pui8Data, uint32_t ui32Size) function in the usvhostenum.c ( Tiware/ usblib).

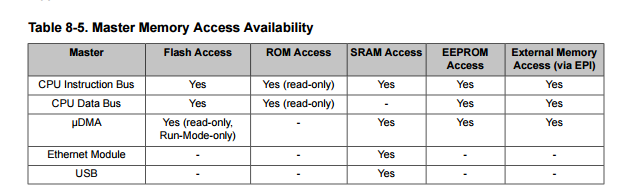

I have tested global heap with external ram with NDK and other TI-RTOS modules and our functions that uses ( malloc and free) with no problems , but

there is this issue with FatFS , so I have to disable Heap in external RAM for it works , that causes memory restrictiions in others modules that use malloc/free internally.