Other Parts Discussed in Thread: EK-TM4C123GXL

Tool/software: Code Composer Studio

The following assembly language project was created using CCS v7 and TI v16.9.1.LTS (v16.9.3.LTS was also tested with the same results):

The .asm file contains:

.global

.text

main:

nop

movw r0, #0x1234

b main

.end

The .cmd file contains:

MEMORY

{

FLASH (RX) : origin = 0x00000000, length = 0x00040000

SRAM (RWX) : origin = 0x20000000, length = 0x00008000

}

SECTIONS

{

.text : > FLASH

}

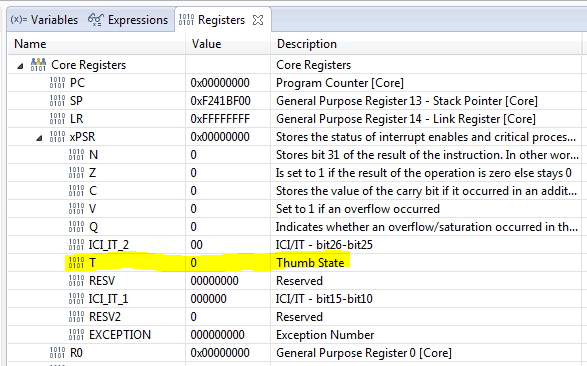

It appears that the CCS debugger launches debug mode with the T bit in the xPSR cleared:

In thumb mode (the Cortex-M4 can only execute in thumb mode), the encoded instructions are:

.global

.text

main:

nop BF00

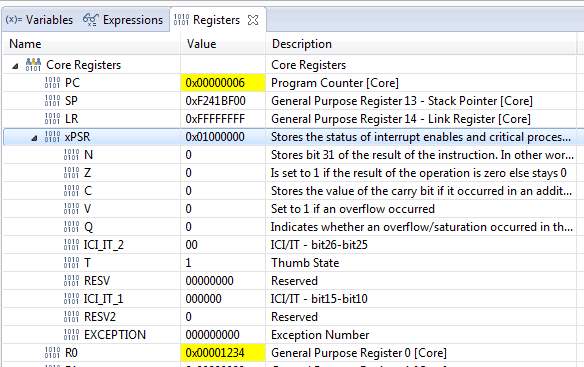

movw r0, #0x1234 F2412034

b main

.end

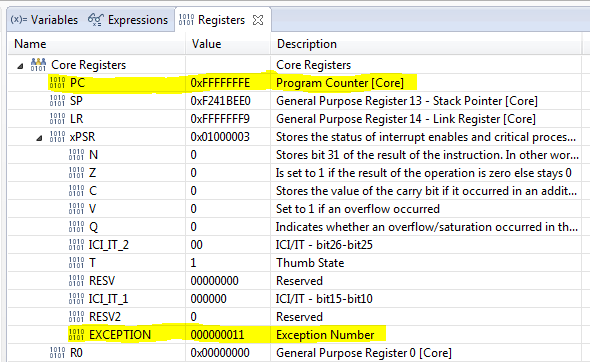

When single-stepping, they are not interpreted properly and exception 11 (0x0B = SVCall) is generated with the PC assigned a value of 0xFFFFFFFE

If the xPSR is modifed before single-stepping from 0x00000000 to 0x01000000 (setting the T bit), then execution is normal. It was observed that the T bit does get set after the exception is generated and if the PC is manually assigned a value of 0, the debugger appears to operate normally.

This sequence does not occur on the MacOS with CCS v7 and TI v16.9.1.LTS

Any assistance with this would be appreciated.