Part Number: TM4C1292NCPDT

Hi,

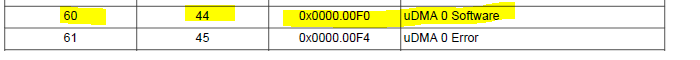

TM4C1292NCPDT is having uDMA supporting 32 channel. I have found in datasheet that its having only one DMA interrupt source number.

I want to use uDMA for two different peripherals(ADC & DAC via SPI interface). How can we define ISR handler for two different peripherals(ADC & DAC via SPI interface) using DMA operation? I believe that DMA will switch the operation among the peripherals based on priority defined. If so how DMA interrupt handler will be identified in Software for different peripherals?

Regards

Bala