Part Number: TM4C129XNCZAD

Hi,

It's almost 2 years that we are producing our boards: MCU TivaC129 + external EPI SDRAM (for frame buffer).

We've choosen SDRAM ESMT M12L64164A(2Y) for our purpose and all was fine.

Now we've produced 6 samples with new SDRAM Alliance AS4C4M16SA, because there are some problems to find the above part number.

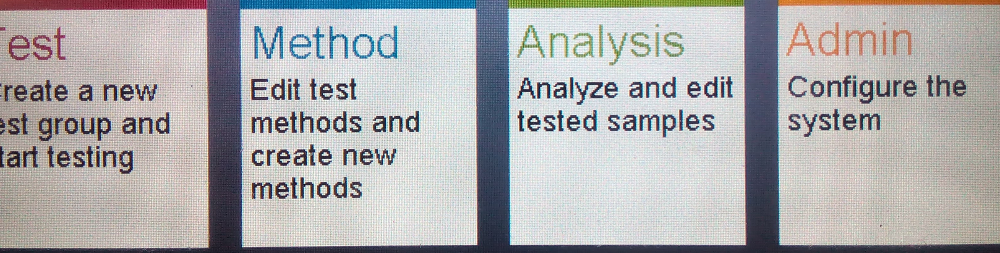

The main problem we have discovered is that the LCD screen shows light blue vertical lines with the same firmware.

We choosen the Alliance memory, because from datasheet they have almost the same characteristics of ESMT, but now we are not so sure that the 2 SDRAM are compatible.

Attached to this post, the timing table e the screenshot of the defect we obtain with new SDRAM.

What's going wrong?

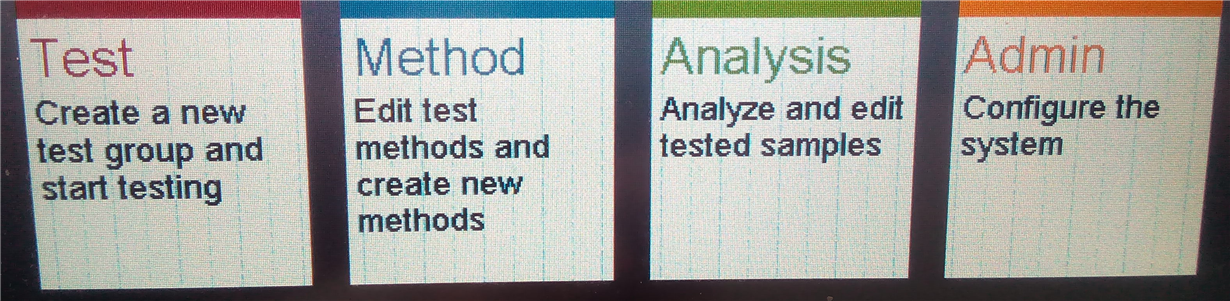

The good image is: