Part Number: TM4C1290NCPDT

Customer running with 25MHz Crystal and trying to determine it's impact TM4C1290NCPDT PLL stability/drift and how it impacts CAN Controller to answer the following:

For PLL's record max drift. If a PLL is being used record tolerance of the PLL and base oscillator

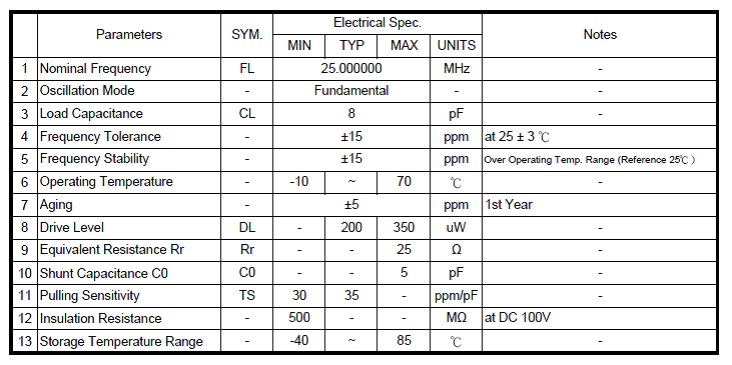

with a 25MHz crystal with the following specification

They are worried that based on their calculation there is a 1% drift which violates the CAN protocol of +/- 0.4% at 500K CAN. The PLL is configured for 480MHz, M = 96, N = 5, reference frequency 5MHz