I am trying to interface my TM4C123G launchpad with an MCP23S17 Bus Expander. Presently, I am trying to read a configuration register at address 0x00. The datasheet on the bus expander states:

The SPI write operation is started by lowering CS. The

Write command (slave address with R/W bit cleared) is

then clocked into the device. The opcode is followed by

an address and at least one data byte.

The SPI Addressing is indicated as 0 1 0 0 ADR2 ADR1 ADR0 R/W A7 A6 A5 A4 A3 A2 A1 A0. Using HW adsressing 000, so we have a uint32_t that is coded to 0x4100 (Address 0, Read=1) and register address 0x00.

SSIDataPut(SSI0_BASE, 0x4100);

while (SSIBusy(SSI0_BASE));

SSIDataGet(SSI0_BASE, rxData);

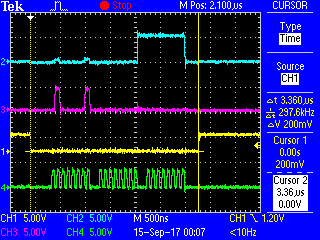

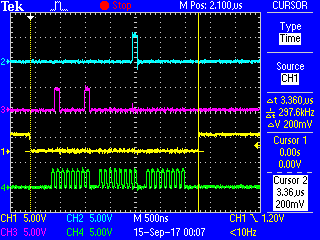

There is 16 clock pulses and the output data is good, but then the clock stops. Every so often, the input data comes in during the next transmit. We have been experimenting with trying to send extra bytes to keep the clock active, but we can not get it to work reliably. I am able to change the address and see the same results with other registers returning the POR default values. Help please! Thanks

Looking at the scope, the *CS is good and I see the output SSI0 TX with the 0x4100. This is immediately followed by a SSIDataGet().