My customer has a major concern regarding the TM4C129.

There were previous issues with the CAN operation, which we concluded was due to PCB contamination during PCB assembly. We have not seen this failure on a sample of the cleaner PCBs.

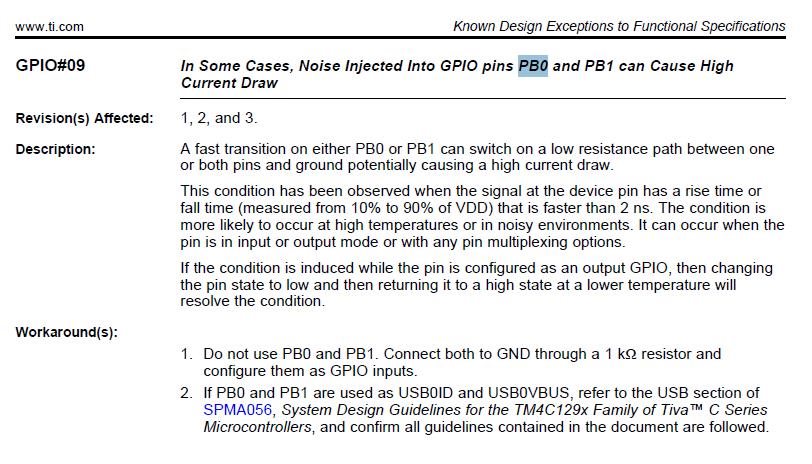

However, reading through the TI errata for the uP and found the following;

Our design has the CAN RX and TX on PB0 & PB1

we are now concerned

1/ that the PCBA cleanliness issue masked an underlying problem which could occur again in the future?

2/ The Ti solution implies that the fix is to not use the PB0 or PB1 pins, unless they are for USB and follow the design guides.

Would you be able to comment if PB0 or PB1 can be used for CAN? The errata implies it cannot if the rise times are fast. please help clarify???