Part Number: EK-TM4C129EXL

Other Parts Discussed in Thread: EK-TM4C1294XL, UNIFLASH

Tool/software: Code Composer Studio

Hi everybody,

I have the EK-TM4C129EXL Launchpad (I use the on board Stellaris debug Interface) and I downloaded my own software on it, which, among others has a USB Host Interface implemented. I was doing tests and debugging the software with CCS and everything was doing fine. At some point, I connected the USB to test the communication and wanted to debug. Since then the CCS Shows: "Error connecting to the target", when the Firmware has to be downloaded on the chip. Since then, I cannot debug anymore, but the software on the MCU is running...

I tried to erase the flash with the LM Flash Programmer but I get the error "**ERROR**: Unable to initialize target -0!"

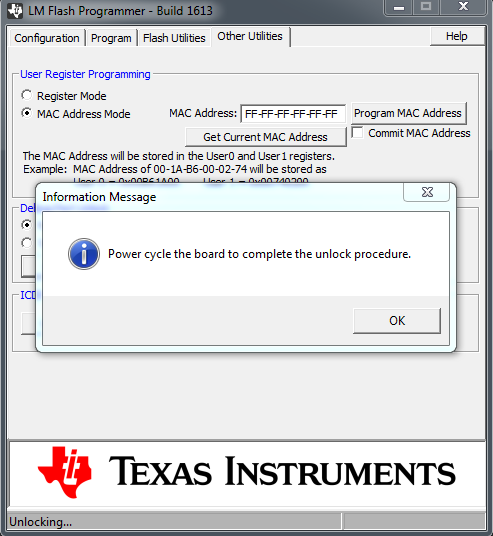

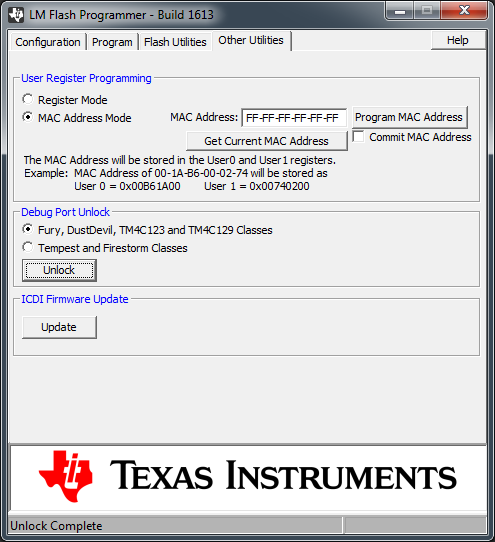

Then I unlocked the MCU using the LM Flash Programmer Debug Port Unlock Utility. The process was finished successfully.

I still get the error with the LM Flash programmer when I want to erase the Flash or with the CCS when I want to load my program.

Hence, I have a software running on my MCU, but I cannot download a Firmware anymore.

Do you have any idea what the Problem could be??

Thanks a lot in advance!!

Greetings,

Sara