Tool/software: TI C/C++ Compiler

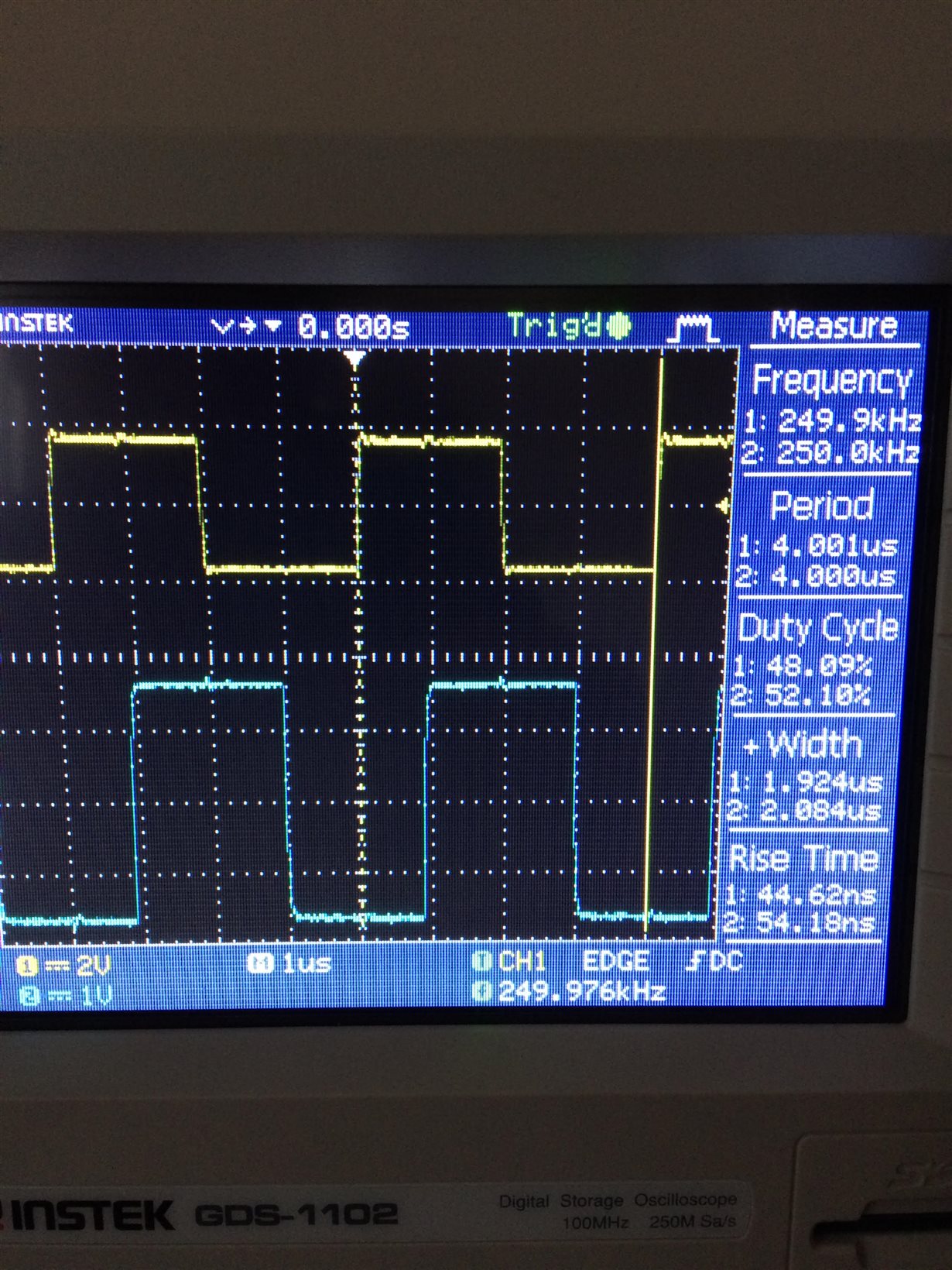

How can I produce a deadtime that will be 20 percent of the pwm period ?

where do i make mistakes ?

#include <stdint.h>

#include <stdbool.h>

#include "inc/hw_memmap.h"

#include "inc/hw_types.h"

#include "driverlib/sysctl.h"

#include "driverlib/gpio.h"

#include "driverlib/debug.h"

#include "driverlib/pwm.h"

#include "driverlib/pin_map.h"

#include "inc/hw_gpio.h"

#include "driverlib/rom.h"

int main(void)

{

uint32_t cycle;

uint32_t pwmfrequency;

uint32_t deadband;

uint32_t pwmperiod;

pwmperiod=50;

pwmfrequency=SysCtlPWMClockGet()/pwmperiod;

deadband=pwmperiod*20/100;

cycle=pwmperiod*50/100;

SysCtlClockSet(SYSCTL_SYSDIV_1|SYSCTL_USE_PLL|SYSCTL_OSC_MAIN|SYSCTL_XTAL_16MHZ);

SysCtlPWMClockSet(SYSCTL_SYSDIV_8);

SysCtlPeripheralEnable(SYSCTL_PERIPH_PWM0);

SysCtlPeripheralEnable(SYSCTL_PERIPH_PWM1);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOE);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOD);

GPIOPinTypePWM(GPIO_PORTE_BASE,GPIO_PIN_4);

GPIOPinTypePWM(GPIO_PORTE_BASE,GPIO_PIN_5);

GPIOPinTypePWM(GPIO_PORTD_BASE,GPIO_PIN_0);

GPIOPinTypePWM(GPIO_PORTD_BASE,GPIO_PIN_1);

GPIOPinConfigure(GPIO_PE4_M0PWM4);

GPIOPinConfigure(GPIO_PE5_M0PWM5);

GPIOPinConfigure(GPIO_PD0_M1PWM0);

GPIOPinConfigure(GPIO_PD1_M1PWM1);

PWMGenConfigure(PWM0_BASE,PWM_GEN_2,PWM_GEN_MODE_UP_DOWN|PWM_GEN_MODE_NO_SYNC);

PWMGenConfigure(PWM1_BASE,PWM_GEN_0,PWM_GEN_MODE_UP_DOWN|PWM_GEN_MODE_NO_SYNC);

PWMGenPeriodSet(PWM0_BASE, PWM_GEN_2,pwmperiod);

PWMGenPeriodSet(PWM1_BASE, PWM_GEN_0,pwmperiod);

PWMDeadBandEnable(PWM0_BASE,PWM_GEN_2,deadband,0); // pd1

//PWMDeadBandEnable(PWM1_BASE,PWM_GEN_0,deadband,0); // pe4

PWMOutputState(PWM0_BASE, PWM_OUT_4_BIT,true);

PWMOutputState(PWM0_BASE, PWM_OUT_5_BIT,false);

PWMOutputState(PWM1_BASE, PWM_OUT_0_BIT,false);

PWMOutputState(PWM1_BASE, PWM_OUT_1_BIT,true);

PWMGenEnable(PWM0_BASE, PWM_GEN_2);

PWMGenEnable(PWM1_BASE, PWM_GEN_0);

while(1)

{

PWMOutputInvert(PWM0_BASE,PWM_OUT_4_BIT,true);

PWMPulseWidthSet(PWM0_BASE, PWM_OUT_4,cycle);

// PWMPulseWidthSet(PWM0_BASE,PWM_OUT_5,cycle);

//PWMPulseWidthSet(PWM1_BASE,PWM_OUT_0,cycle);

PWMPulseWidthSet(PWM1_BASE,PWM_OUT_1,cycle);

}

}