Tool/software: TI-RTOS

Hi.

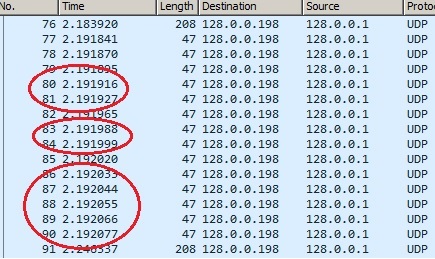

I use TM4C1294NCPDT chip in my Ethernet application. When I send several(15) short(47 bytes) frames with a high frame's frequency (10-14 uSec between frames) from Host computer to my controller, the controller misses some frames.

When I decrease frames frequency(make a little delay between the packets) the controller doesn't miss the frames.

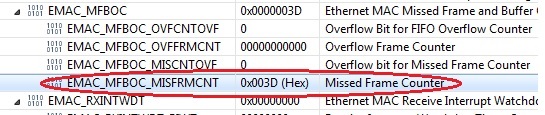

I found, that frames are missed when they are moved from RX FIFO of Ethernet controller to RAM, by Ethernet's DMA. ("Missed Frame Counter" bits of EMACMFBOC register increases when I send these packets).

From chip's datasheet:

Missed Frame Counter - This field indicates the number of frames missed by the controller because of the Host Receive Buffer being unavailable. This counter is incremented each time the DMA discards an incoming frame. This counter is cleared when the DMA accepts frames.

What could be the reason?

Is there a restriction on "Inter Packet Gap" for TIVA?

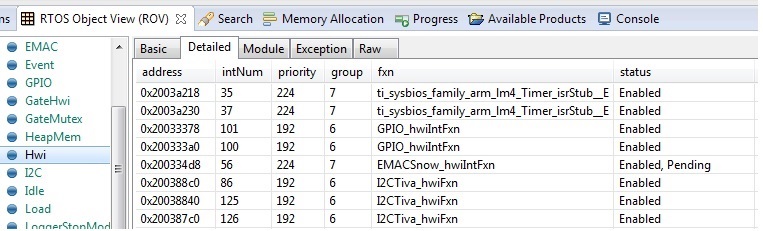

I use in my application TI-RTOS and NDK networking stack. The Ethernet works 100 Mbps.

Thanks in advance.