Dear Ti,

We have below concerns during using TM4C and need your help to advise.

There are 2 boards:

- MCU board (only MCU + BT5 chip)

- Motherboard (industrial interface (4-20mA, 0-10V, I/O, Ethernet)

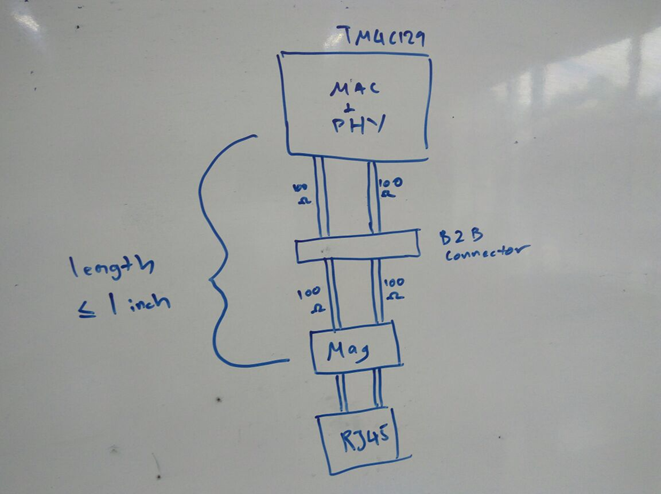

MCU board is connected to motherboard by high speed B2B connector. Note that the motherboard has no MCU/MPU.

We have concern on differential pairs routing from the Magnetics+RJ45 (Magjack) to the B2B connector then to TM4C129x (PHY pins).

1. use TM4C internal PHY – magjack is at motherboard

2. use ordinary MCU and place external PHY at motherboard

Detailed explanation as below.

We would like to know whether the configuration below will affect the Ethernet performance and produce interference?

or is it better to use an external PHY IC as shown in the picture below:

What we understand is that the RMII/MII signals are less susceptible to noise, and the routing of RMII/MII through the B2B connectors should cause less problems.

Please help to advise further.