Other Parts Discussed in Thread: EK-TM4C1294XL, TPD4S012, , TM4C1294NCPDT, TPS2052B

After a few times plugging in USB0 OTG port cable the entire MCU may suddenly POR for no good reason.

Suspecting VBUS the only 5 volt tolerant pin (PB1) not being protected by a 5v zener diode or even a series resistor to PB1 while plugging cable into USB hub port.

When we follow the TI schematic EK-TM4C1294XL for proper USB port design and destroy two MCU's ($28.00) plus the time to install/remove burned out ones, that is an issue!

Both MCU tested did the very same POR resulting in MCU temperature getting smoking hot over the USB input area, perhaps a sign of poor schematic example for proper USB port layout?

Note worthy TPD4S012 (4 channel) ESD suppressor for USB signals datasheet fails to properly identify pin 1 orientation and uses a bottom pad view of pin 1, no installer on earth can ever see through a plastic chip. The chip is so small that even at 8 diopter magnification one can barely make out a white dot mid center near pin 1 side and a dimple on the opposite corner anyone might assume pin 1, but is not pin 1.

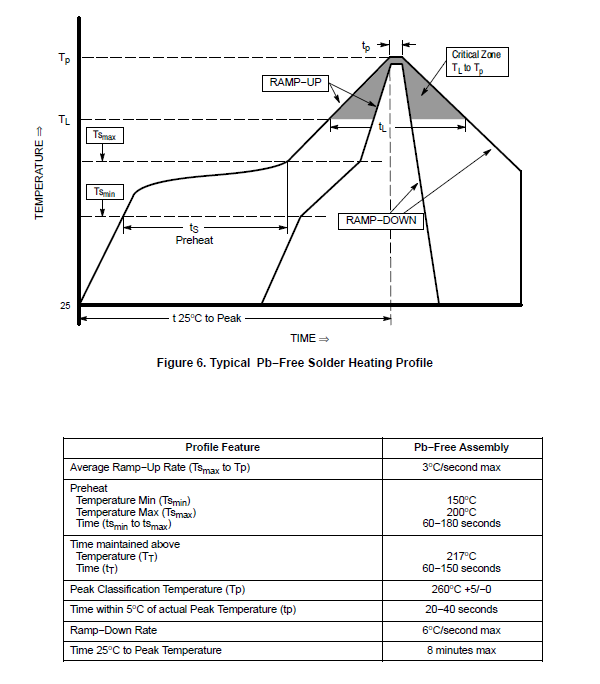

That is according to how TI installed the very same IC on the EK-TM4C1294XL we used to insure the ESD protection chip was installed in the proper orientation. There is also no reflow or pin soldering temperatures listed in datasheet but we kept air flow below 245*C for 10 seconds. It doesn't have any resistive shorts to ground or any other adjacent pins.

How is a 16v zener TPD4S012 protecting the TM4C1294KCPDT VBUS input?

8.2.2.1 Signal Range on D+, D-, ID and VBUS pins:

The TPD4S012 has 3 pins which support 0 to 5.5 V signals, these are suited for the D+, D–, and ID pins. The

VBUS pin is suitable for the VBUS line, and has the benefit of being tolerant of voltages up to 16 V