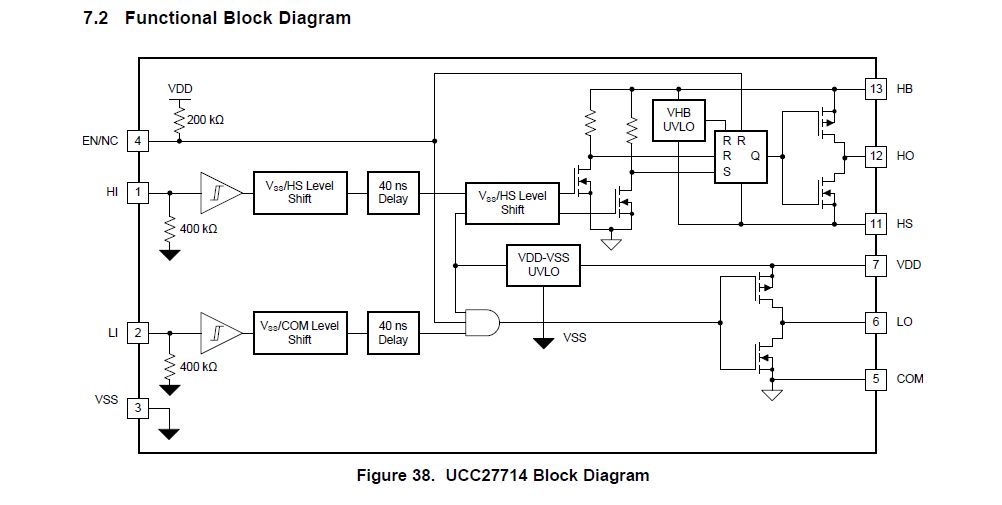

Other Parts Discussed in Thread: UCC27714, LM339,

Register 21: GPIO Analog Mode Select (GPIOAMSEL), offset 0x528

Important: This register is only valid for ports and pins that can be used as ADC AINx inputs. If any pin is to be used as an ADC input, the appropriate bit in GPIOAMSEL must be set to disable the analog isolation circuit. The GPIOAMSEL register controls isolation circuits to the analog side of a unified I/O pad. Because the GPIOs may be driven by a 3.3-V source and affect analog operation, analog circuitry requires isolation from the pins when they are not used in their analog function.

*******************************************************************

Register 10: GPIO Alternate Function Select (GPIOAFSEL), offset 0x420

The GPIOAFSEL register is the mode control select register. If a bit is clear, the pin is used as a GPIO and is controlled by the GPIO registers. Setting a bit in this register configures thecorresponding GPIO line to be controlled by an associated peripheral. Several possible peripheral functions are multiplexed on each GPIO. The GPIO Port Control (GPIOPCTL) register is used to select one of the possible functions.

0 The associated pin functions as a GPIO and is controlled by the GPIO registers.

1 The associated pin functions as a peripheral signal and is controlled by the alternate hardware function.

************************************************************************************************************************

Register 22: GPIO Port Control (GPIOPCTL), offset 0x52C

The GPIOPCTL register is used in conjunction with the GPIOAFSEL register and selects the specific

peripheral signal for each GPIO pin when using the alternate function mode. Most bits in the

GPIOAFSEL register are cleared on reset, therefore most GPIO pins are configured as GPIOs by

default. When a bit is set in the GPIOAFSEL register, the corresponding GPIO signal is controlled

by an associated peripheral. The GPIOPCTL register selects one out of a set of peripheral functions

for each GPIO, providing additional flexibility in signal definition.

So ADC0/1 are not classified as peripherals thereby necessitating setting of AFSEL bits for ANIx input pins?

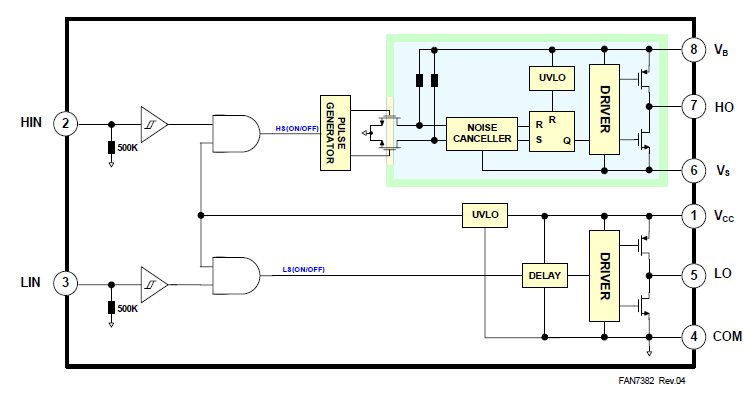

How did Tivaware peanut butter get into UCC27714 chocolate signals?

We have been trying to track down how PWM generator pulse periods seem to occur (phantom) on GPIO peripheral pins, when not being instructed by the application. Often these phantom peanut butter pulses are mirror copies of intended chocolate pulses application sent via PWM peripheral configured GPIO pins. The PWM pins action results are being monitored via ANIx channels and Special Analog inputs of the MCU. Peanut butter pulses (sticky) can oddly end up inverted below ground or as a single rouge phantom pulse thus triggering an external device to drive a damaging pulse. Other TI forum gurus can not understand how such a damaging pulse can occur if the application did not instruct the pulse to be created. Otherwords the peanut butter pulses cause unclassified eratta in the chocolate driven external IC device.

The evidence of GPIO pin isolation barrier break down is indicated via numerous scope captures. All evidence of barrier break down seems contrary to REG 21 claim that the barrier should be disabled rather than enabled for ANIx pins. Alternatively for special analog device inputs in table 10-2, why would they be any different than ANIx pins?

It would make sense to disable the isolation barrier for digital pins when the DEN bit is set or AFSEL bits set too, for a peripherals digital function. However clearing AFSEL bits (REG10) suggest a Special pin be under GPIO register control and AMSEL bit being set for ANIx channels disables the isolation circuit barrier.

All ANIx pins appear correctly configured verified CCS debug, according above documentaion. However the MCU analog isolation brarrier is failing to isolate digital I/O from analog inputs for what ever reasons! If AFSEL bits are cleared for ANIx pins does that not remove the isolation barrier in the GPIO unified I/O pad also shared by Digital pins?

Does it not sound odd to disable an analog barrier on ANXi pins or special funciton analog pins?