Hi Champion

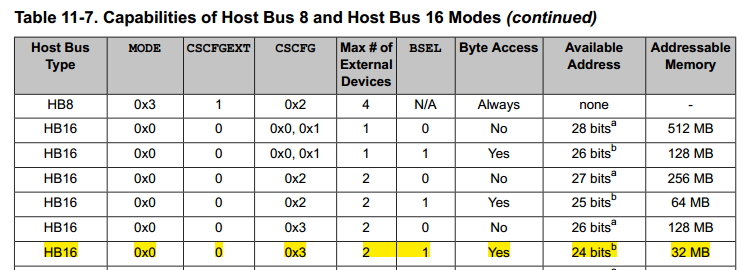

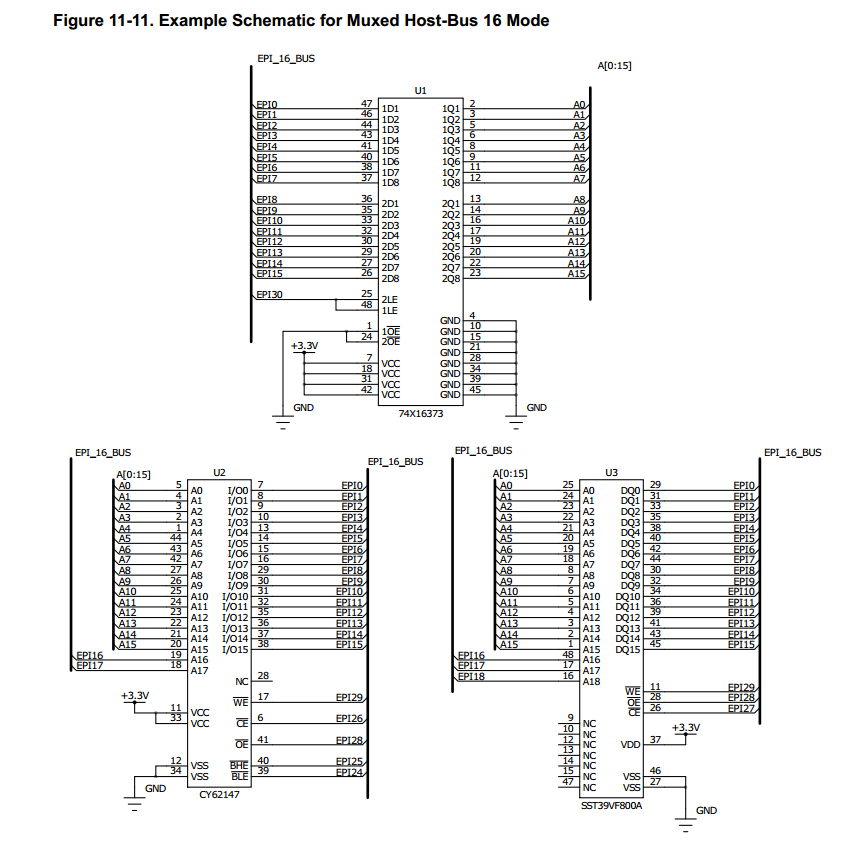

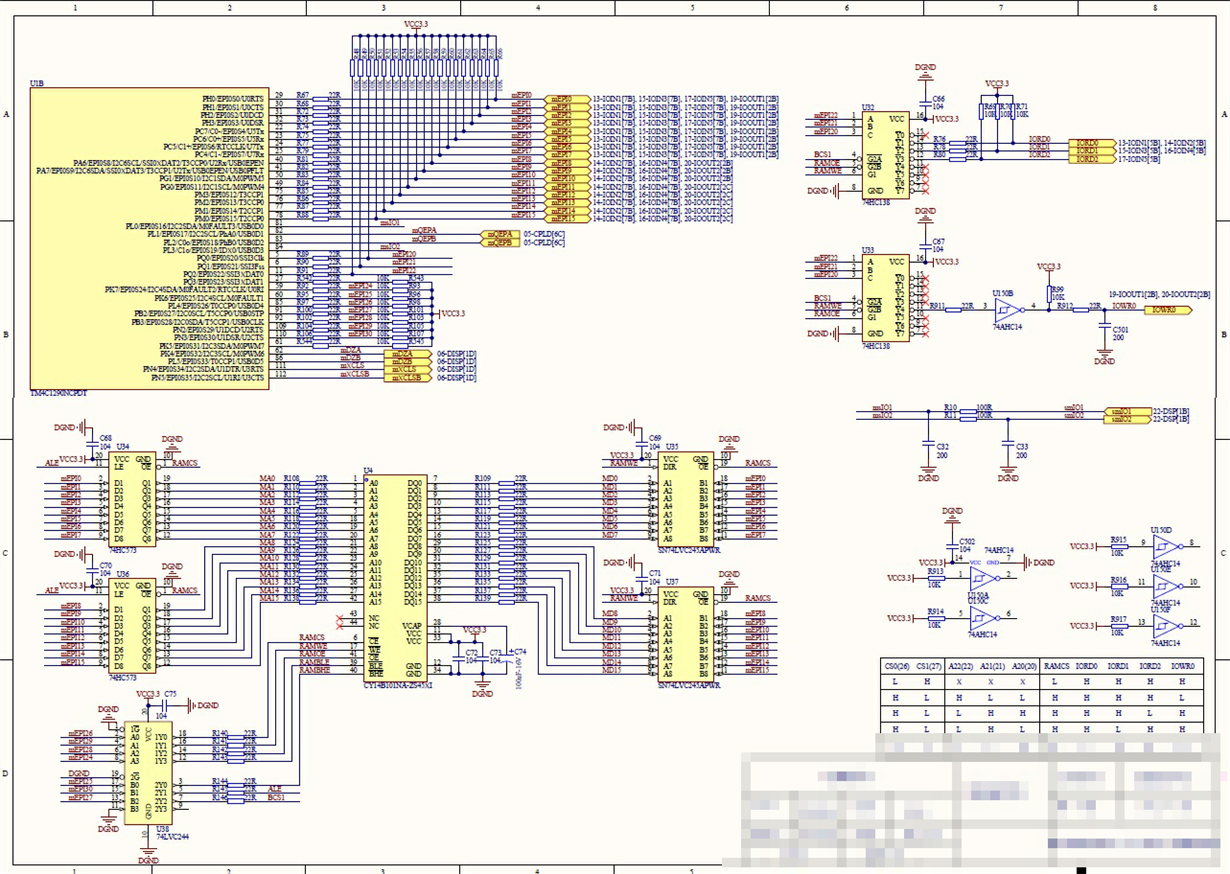

My customer used M4 EPI to access SRAM in host bus16 ADMUX mode, they used the setting as below, and the EPI initialization as below:

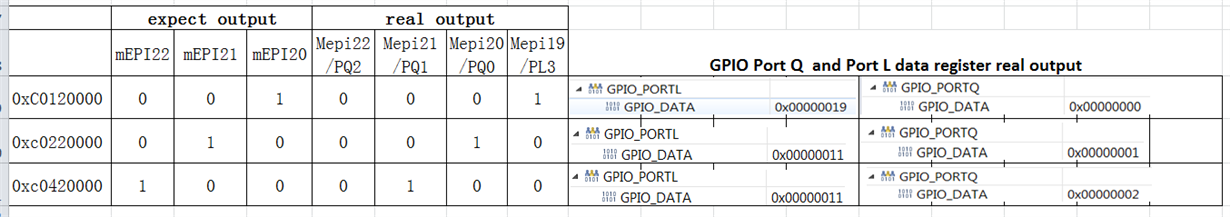

They found when they access the address, it looks the address need to let shif 1 bit to get the correct output, as below test result.

I also test in TM4C129X DK board and get the same result as customer see in their board.

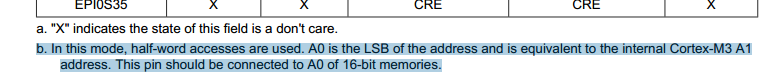

But we didn't find in the datasheet that the least bit address is not A0, so please give your comments on the problem, Thank you.

I attached the whole project when I test in the DK board.

void Epi_Initialize(void)

{

// Enable all the GPIO peripherals.

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOB);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOC);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOD);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOE);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOF);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOG);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOH);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOJ);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOK);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOL);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOM);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPION);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOP);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOQ);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOR);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOS);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOT);

ROM_GPIOPinConfigure(GPIO_PH0_EPI0S0);

ROM_GPIOPinConfigure(GPIO_PH1_EPI0S1);

ROM_GPIOPinConfigure(GPIO_PH2_EPI0S2);

ROM_GPIOPinConfigure(GPIO_PH3_EPI0S3);

GPIOPinTypeEPI(GPIO_PORTH_BASE,GPIO_PIN_0|GPIO_PIN_1|GPIO_PIN_2|GPIO_PIN_3);

ROM_GPIOPinConfigure(GPIO_PC7_EPI0S4);

ROM_GPIOPinConfigure(GPIO_PC6_EPI0S5);

ROM_GPIOPinConfigure(GPIO_PC5_EPI0S6);

ROM_GPIOPinConfigure(GPIO_PC4_EPI0S7);

GPIOPinTypeEPI(GPIO_PORTC_BASE,GPIO_PIN_7|GPIO_PIN_6|GPIO_PIN_5|GPIO_PIN_4);

ROM_GPIOPinConfigure(GPIO_PA6_EPI0S8);

ROM_GPIOPinConfigure(GPIO_PA7_EPI0S9);

GPIOPinTypeEPI(GPIO_PORTA_BASE,GPIO_PIN_6|GPIO_PIN_7);

ROM_GPIOPinConfigure(GPIO_PG1_EPI0S10);

ROM_GPIOPinConfigure(GPIO_PG0_EPI0S11);

GPIOPinTypeEPI(GPIO_PORTG_BASE,GPIO_PIN_1|GPIO_PIN_0);

ROM_GPIOPinConfigure(GPIO_PM3_EPI0S12);

ROM_GPIOPinConfigure(GPIO_PM2_EPI0S13);

ROM_GPIOPinConfigure(GPIO_PM1_EPI0S14);

ROM_GPIOPinConfigure(GPIO_PM0_EPI0S15);

GPIOPinTypeEPI(GPIO_PORTM_BASE,GPIO_PIN_3|GPIO_PIN_2|GPIO_PIN_1|GPIO_PIN_0);

ROM_GPIOPinConfigure(GPIO_PQ0_EPI0S20);

ROM_GPIOPinConfigure(GPIO_PQ1_EPI0S21);

ROM_GPIOPinConfigure(GPIO_PQ2_EPI0S22);

GPIOPinTypeEPI(GPIO_PORTQ_BASE,GPIO_PIN_0|GPIO_PIN_1|GPIO_PIN_2);

ROM_GPIOPinConfigure(GPIO_PK7_EPI0S24);

ROM_GPIOPinConfigure(GPIO_PK6_EPI0S25);

GPIOPinTypeEPI(GPIO_PORTK_BASE,GPIO_PIN_7|GPIO_PIN_6);

ROM_GPIOPinConfigure(GPIO_PL4_EPI0S26);

GPIOPinTypeEPI(GPIO_PORTL_BASE,GPIO_PIN_4);

ROM_GPIOPinConfigure(GPIO_PB2_EPI0S27);

ROM_GPIOPinConfigure(GPIO_PB3_EPI0S28);

GPIOPinTypeEPI(GPIO_PORTB_BASE,GPIO_PIN_2|GPIO_PIN_3);

ROM_GPIOPinConfigure(GPIO_PN2_EPI0S29);

ROM_GPIOPinConfigure(GPIO_PN3_EPI0S30);

GPIOPinTypeEPI(GPIO_PORTN_BASE,GPIO_PIN_2|GPIO_PIN_3);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_EPI0);

ROM_EPIModeSet(EPI0_BASE,EPI_MODE_HB16);

ROM_EPIConfigHB16Set(EPI0_BASE,EPI_HB16_CSCFG_ALE_DUAL_CS,0xff);

ROM_EPIDividerCSSet(EPI0_BASE, 0, 2); // divide by 4 , 30Mhz , SdRam

ROM_EPIDividerCSSet(EPI0_BASE, 1, 2);

//ROM_EPIDividerCSSet(EPI0_BASE, 1, 118); // divide by 120 , 1Mhz , IO

ROM_EPIConfigHB16CSSet(EPI0_BASE, 0, EPI_HB16_MODE_ADMUX | EPI_HB16_ALE_HIGH | EPI_HB16_BSEL | 0x0000FF00);

ROM_EPIConfigHB16CSSet(EPI0_BASE, 1, EPI_HB16_MODE_ADMUX | EPI_HB16_ALE_HIGH | EPI_HB16_BSEL | 0x07000000);

ROM_EPIConfigHB16TimingSet(EPI0_BASE, 0, EPI_HB16_PSRAM_256 | EPI_HB16_CAP_WIDTH_2);

ROM_EPIConfigHB16TimingSet(EPI0_BASE, 1, EPI_HB16_PSRAM_256 | EPI_HB16_CAP_WIDTH_2);

ROM_EPIAddressMapSet(EPI0_BASE,

(EPI_ADDR_CODE_SIZE_256B|

EPI_ADDR_CODE_BASE_NONE|

EPI_ADDR_PER_SIZE_16MB|

EPI_ADDR_PER_BASE_C|

EPI_ADDR_RAM_SIZE_256B|

EPI_ADDR_RAM_BASE_NONE

)

);

}