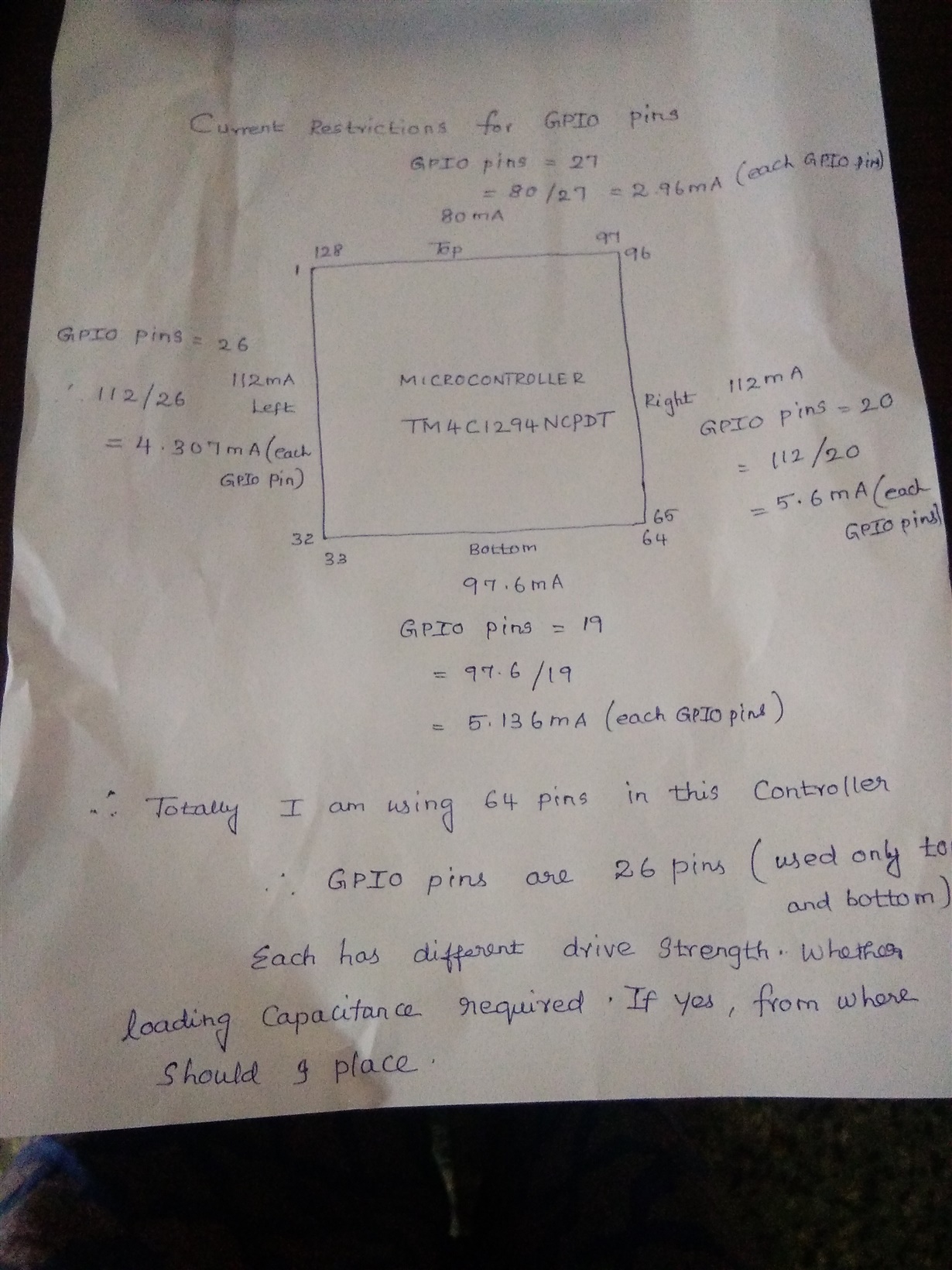

Part Number: TM4C1294NCPDT

Hi Sir,

I am going to design a power circuit to my board. I have gone through the data sheet about current restriction. They specifically mentioned for each side of cumulative current for GPIO pins. In TM4C1294NCPDT datasheet, page no. 1822 mentioned about the I/O reliability and page no. 1823 mention the load condition for the GPIO pin. I couldn't understand, for which pin i need to add the capacitive loading.