Hi,

I am trying to communicate with a certain I2C based IC and wanted to read some values from a register. The procedure to read page over I2C is to first send write command to the salve address followed by the register no. which will be acknowledged by the slave, then without sending the stop condition, send the read command with the slave address which will be again acknowledged by the slave . After that we need to send the burst read command to continuously read slave data and in the end master will acknowledge and send the stop bit.

I attempted at doing this with the following piece of code. However, I am not getting proper acknowledges and sometimes the data which I try to write in register is corrupted. What am I doing wrong?

//

// To read the power consumed

//

void I2C8ReadPower(uint8_t ui8SlaveAddr )

{

uint32_t error = 0;

//

// Set the slave address for the I2C Base

//

I2CMasterSlaveAddrSet(I2C8_BASE, ui8SlaveAddr, false);

//

// Send the I2C address bus(power) and the register value to be read

// on the I2c Bus.

//

I2CMasterDataPut(I2C8_BASE, READ_POWER_ADDRESS);

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_SEND_START);

SysCtlDelay(10000);

while (I2CMasterBusy(I2C8_BASE))

{

}

error |= I2CMasterErr(I2C8_BASE);

if (error == 0x16)

{

//

// Arbitration error

//

while (1)

{}

}

//

// Read the power

//

I2CMasterSlaveAddrSet(I2C8_BASE, ui8SlaveAddr, true);

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_RECEIVE_START);

SysCtlDelay(10000);

while(I2CMasterBusy(I2C8_BASE))

{

}

gui8_power[2] = I2CMasterDataGet(I2C8_BASE);

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_RECEIVE_CONT);

SysCtlDelay(10000);

while(I2CMasterBusy(I2C8_BASE))

{

}

gui8_power[1] = I2CMasterDataGet(I2C8_BASE);

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_RECEIVE_FINISH);

SysCtlDelay(10000);

while(I2CMasterBusy(I2C8_BASE))

{

}

gui8_power[0] = I2CMasterDataGet(I2C8_BASE);

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_SEND_STOP);

SysCtlDelay(10000);

while(I2CMasterBusy(I2C8_BASE))

{

}

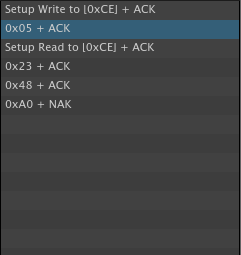

Here, the Logic analyser result is:

The data in front of 0x23 and 0x48 should be NAck and 0XA0 should be acknowledged by the master