Tool/software: Code Composer Studio

Hi,

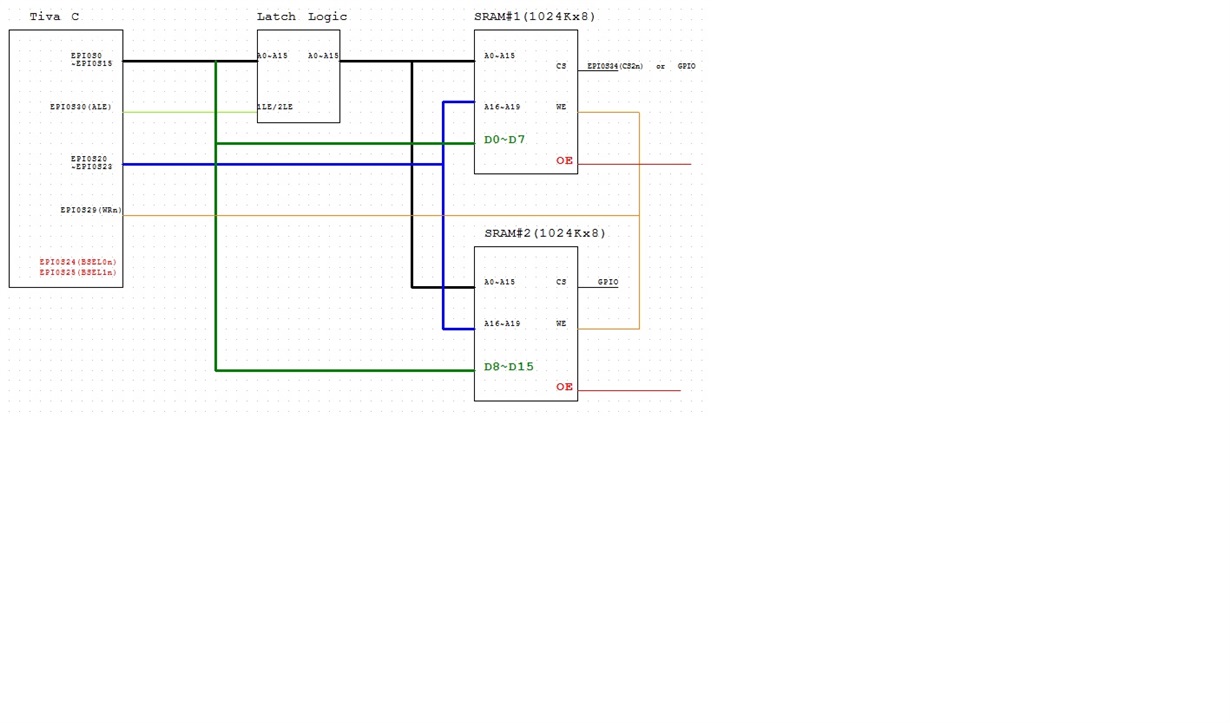

We have confirmed that TM4C1299 will connect cypress SRAM CY62158EV30(1024Kx8). The TM4C1299 still works on Host Bus 16-bit Muxed Interface mode and will connects two CY62158EV30 for 1 bank. Totally we will have 4 banks for this product. I want to know how to deal with the EPI0S24(BSEL0n)&EPI0S25(BSEL1n)? The SRAM doesn't have this two pin.