Part Number: EK-TM4C1294XL

Other Parts Discussed in Thread: LM94022

Projected in other post not yet receiving an answer;

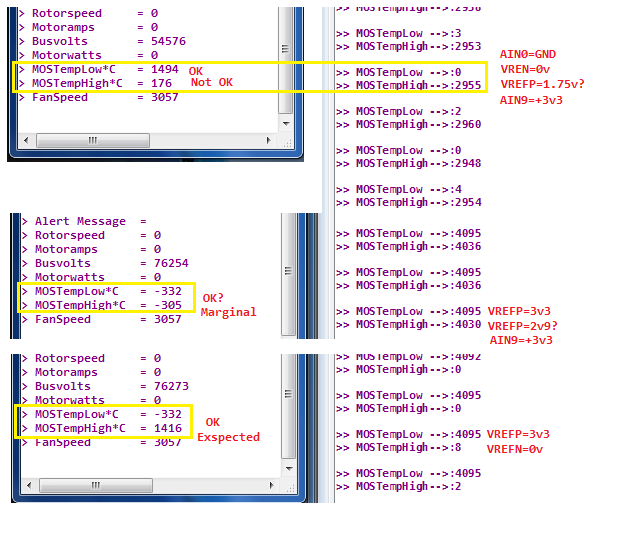

Why multiple AINx channels with the very same VREFP 3v3 signal step 0 conversion is (4095) yet step 1-END produce >-30 LSB from step 0 results.

This issue FIFO reads relative to VREFP cascade in all sequencers being tested. Similar conversion results occur steps 1-END being -30 LSB, further ascending >30 LSB downward as step 0 remains constant 4095. Sometimes step 1-END FIFO results are divided almost in half or don't even produce any conversion relative to the AINx sample in step 2 no matter the step of END IE.

The problem seems to worsen as the sequencer trigger source is accelerated via GPTM Oneshot (1.25us) synchronous to 80us intervals or PWM GEN trig count load center of each 80us period. Yet even a 1 second GPTM TriggerProcessor source is being used in the example above causes the same degrading FIFO conversion results.

Is this an known issue, is there any WA other than using a single AINx input step and reconfiguring it on the fly for handling multiple analog input signals?