Part Number: TMS570LC4357

Hi all,

I am currently working with a TI CANFD-To-SPI-Bridge TCAN4550. I programmed the MibSpi transfer groups in a way that they read out all necessary registers from TCAN4550. WIth the help of DMA I want to transfer the CANFD frame's payload into a RAM buffer of 64 Byte.

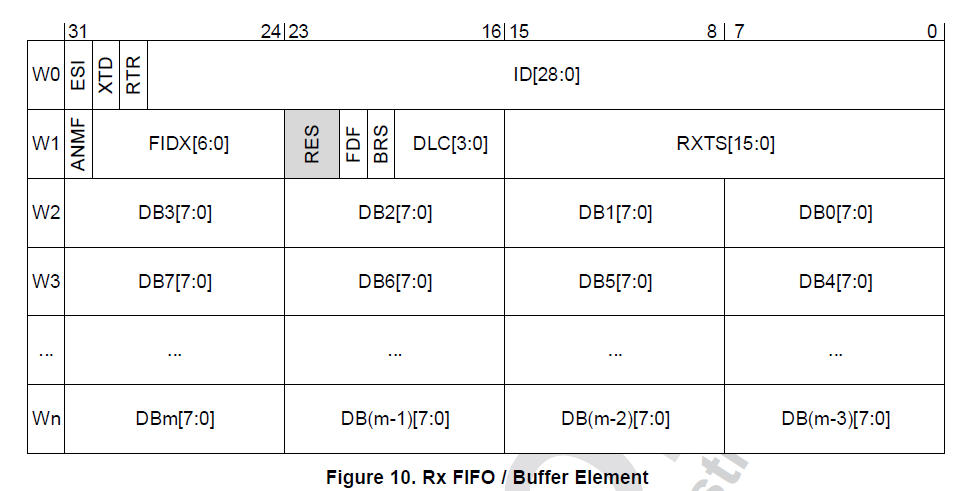

This is how the register looks in TCAN4550

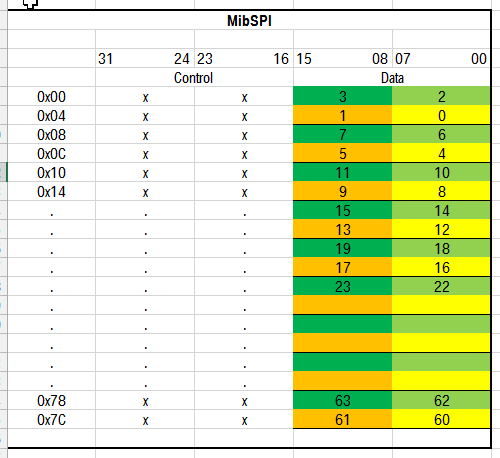

Reading a word from TCAN4550 delivers the bytes from MSB to LSB and from W2 to Wn. Let's say TCAN receives a frame with 64 byte payload, such as byte_0 = 0, byte_1=1 byte_2 = 2 ...... byte_63 = 63.

After reception, the MibSPI RAM looks like this:

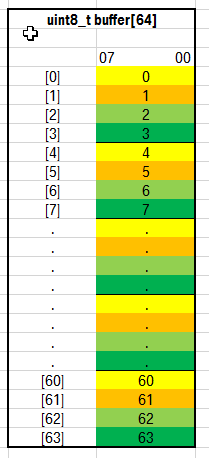

The frame buffer in the application should look like the frame sent on the CAN bus:

After reading the MibSPI and DMA manual I'd say it's not possible to program the DMA controller in a way that it re-orders the MibSPI-RAM into whatever is needed in RAM. Is that correct or is there a solution for it?

Best Regards,

Juergen