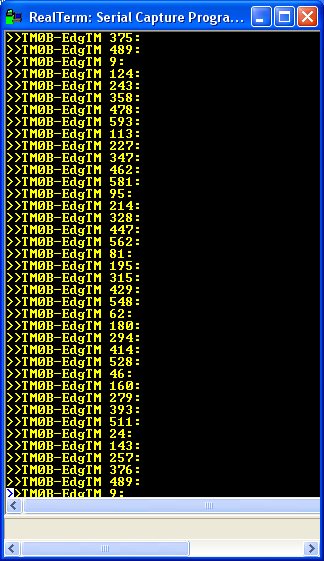

Datasheet section for Edge Time measures seems to typo the snapshot for prescaler register. Snapshot mode registers are for periodic and Oneshot modes as confirmed by register text. The other point is the edge time mode as properly configured does capture events interrupts. The results captured GPTMTnR, GPTMnPR registers return unstable values for stable input signal CCP and POS edge events interrupts. The timer is being configured PIOSC clock source, 25ms down count, positive edge events capture interrupts for 20Hz-220Hz input signal, no real issues here.

Figure 13-3 on page 963 shows how input edge timing mode works. In the diagram, it is assumed that the start value of the timer is the default value of 0xFFFF, and the timer is configured to capture rising edge events. Each time a rising edge event is detected, the current count value is loaded into the GPTMTnR and GPTMTnPS registers, and is held there until another rising edge is detected (at which point the new count value is loaded into the GPTMTnR and GPTMTnPS registers).

Register 24: GPTM Timer B Prescale Snapshot (GPTMTnPS), offset 0x060 For 16-/32-bit wide GPTM, this register shows the current value of the Timer B prescaler for periodic snapshot mode.

Register 15: GPTM Timer B Prescale (GPTMTnPR), offset 0x03C This register allows software to extend the range of the timers when they are used individually. When in one-shot or periodic down count modes, this register acts as a true prescaler for the timer counter. When acting as a true prescaler, the prescaler counts down to 0 before the value in the GPTMTnR and GPTMTnV registers are incremented. In all other individual/split modes, this register is a linear extension of the upper range of the timer counter, holding bits 23:16 in the 16-bit modes of the 16/32-bit GPTM.

13.4.4 Initilization & Configuration text differs with Fig13-3 which states to get the snapshot prescale register GPTMTnPS for the return results. Register GPTMTnPS is 0x0 ever interrupt time!

5. If a prescaler is to be used, write the prescale value to the GPTM Timer n Prescale Register (GPTMTnPR).

Capture Results: