Other Parts Discussed in Thread: EK-TM4C1294XL

Relative to same issue of edge counts unidentified internal noise source; Scenario GPTM0A CCP0 configured 20Khz PWM and GPTM0B CCP1 input edge counts, wire PL4 into PL5 with WPU oddly drags down 4mA PL4 near 2v. Adding Schottky in series PL4 to PL5 produces whisker like 20Khz pulses riding on 3v. Otherwise PL4 (CCP1) counts 49-200Hz edges from external open collector Taco source without issues until other GPTM are later being enabled, GPTM1A and GPTM4A each configured as Oneshot timers, 1A with interrupt vector and 4A as an ADC trigger source to ADC0 SS2. Both GPTM0A/B use alternate PIOSC clock source and have no match events configured lower than 0xD3.

How could PL5 CCP0 input to PL4 WPU pull down the signal? DMM check PL5 has typical 1.7v drop and 6 Megohms to ground. Why would the open collector on PL5 not pull down the signal even though is much slower rate than PL4 20Khz? It seems like PL5 is acting like an bidirectional GPIO port when PL4 PWM signal is input to it.

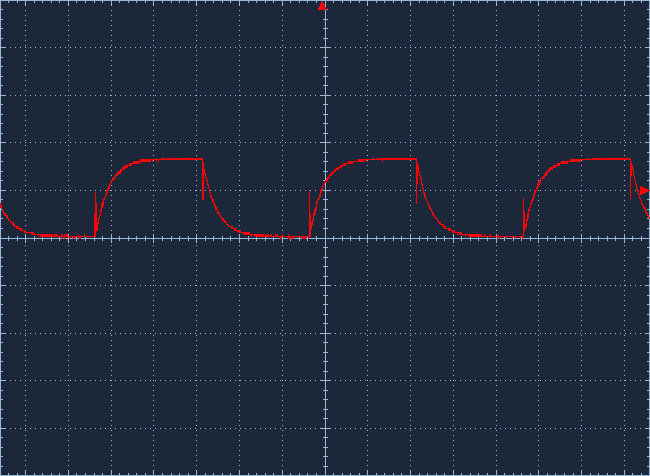

20Khz CCP0 PWM PL4

Open collector Taco source PL5 WPU:

PL4 input to PL5 WPU without open collector signal above: