Part Number: TM4C1294KCPDT

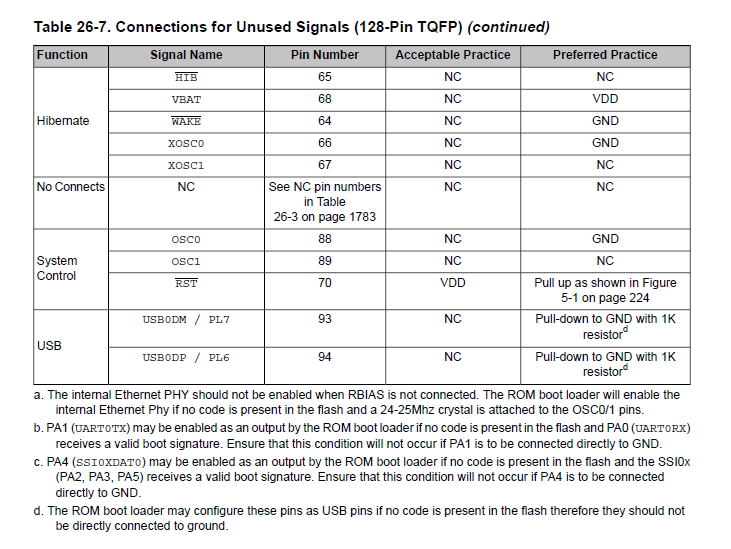

Does errata ELEC#02 relate to unused VBAT preferred practice for unused pins (Table 26-7) VBAT tied to VDD? Should VBAT pin 68 "May be damaged" leads to any other pins being effected such as VDD being pulled down to GND when VBAT has been tied to VDD?

It seems ELEC#02 lists no specific conditions of pin 68 use as previous clarified in datasheet that otherwise seems to contradict Table 26-7. Does an errata hive a higher priority than tables previously defined unused pins practice in the datasheet? If true why has the datasheet Table 26-7 not been corrected to reflect ELEC#02 if such an errata can directly effect VDD? Perhaps pin 68 preferred practice should not be tied to VDD and instead included a series resistor to stop issues from an unused VBAT pin.