Hello Experts,

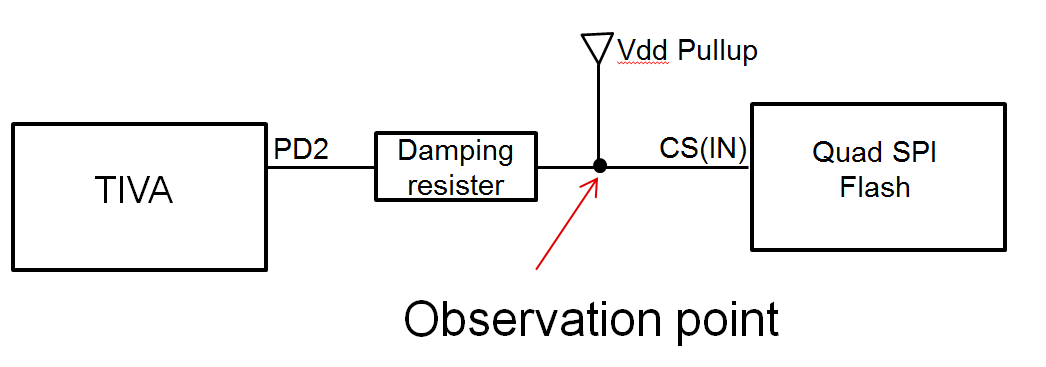

I received inquiry about PD2 terminal(GPIO pin) during Power-down process. Our customer configured PD2 as GPIO/Open-drain and implemented this terminal as follows. The reason why customer configured Open-drain, is that it is easy to implement additional CS (chip select).

Although Our customer was evaluating their system with TM4C1290NCZAD , our customer noticed PD2 terminal indicated low(0V) for split second during system power down. Also, This behavior was observed when /RST was just asserted. I believe BOR(Brown-Out Reset) seems to occur since VDD show around 2.8V. as the result, PD2 is configured as default setting. Can we have your Expert’s comments on this behavior?

Also, if possible, could you elaborate how to avoid this unexpected low transaction , please?

Best regards,

Miyazaki