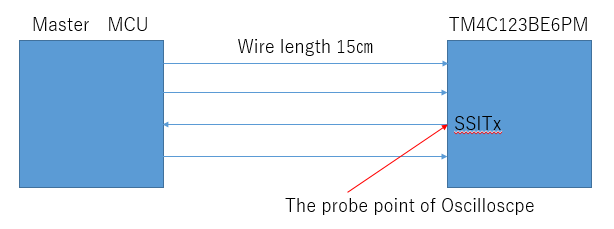

Hello, we are debugging TM4C123BE6 SSI Slave program.

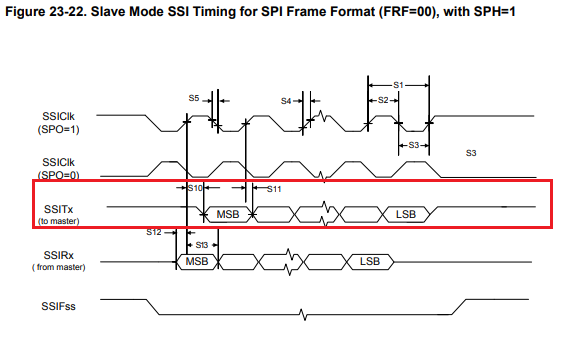

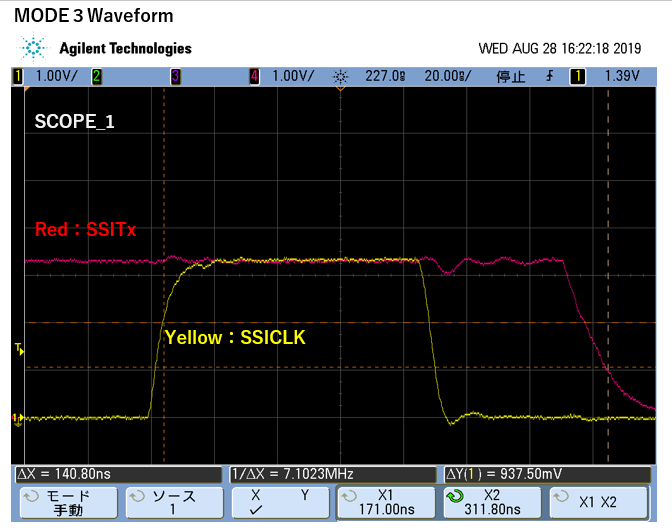

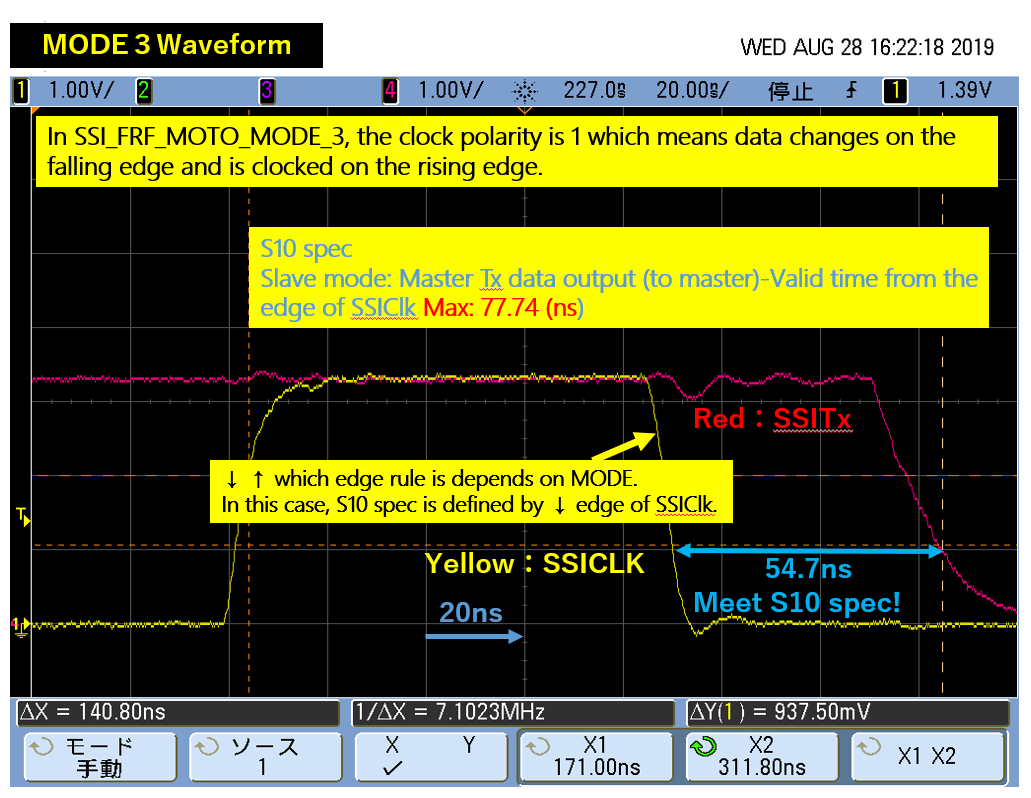

We choose SSI Slave Mode3(SPO=1,SPH=1). But SSITx waveform is different from the Datasheet's description (Figure23-22).

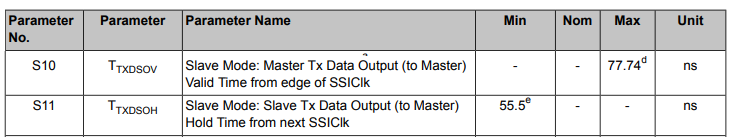

S10 and S11 Values are as follows;

We use the following SSIConfigSetExpClk function.

SSIConfigSetExpClk(SSI0_BASE, SysCtlClockGet(), SSI_FRF_MOTO_MODE_3, SSI_MODE_SLAVE, 6666666, 8);

We want to use SSITx to meet MODE3 (Figure23-22) spec.

If there are any extra S/W settings in order to meet MODE3 spec ,please let me know.

Best regards,

ay0689_3