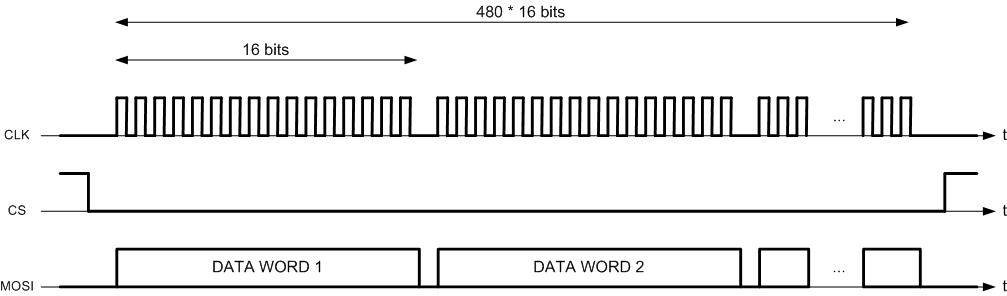

I use SSI interface as SPI slave port. If the master sends words with a chip select pulse for each serial word the reception of every word is ok. But if I try to send a lot of words with one chip select pulse I get a failure: the receiver accepts only one (first?) word from each frame. Words have bit depth as 16 bits. Here are some source codes with my initialization. Could anyone suggest how to receive every word form the multy-word frame with one common chip select pulse?

extern int16_t spiData[N_RAW_BUF], i_wr, i_rd;

void spi0_init(void)

{

uint32_t delay;

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI0);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA);

GPIOPinConfigure(GPIO_PA2_SSI0CLK);

GPIOPinConfigure(GPIO_PA4_SSI0RX);

GPIOPinConfigure(GPIO_PA3_SSI0FSS);

GPIOPinTypeSSI(GPIO_PORTA_BASE, GPIO_PIN_2 | GPIO_PIN_3| GPIO_PIN_4);

for(delay=0; delay<10000; delay++);

SSIConfigSetExpClk(

SSI0_BASE,

80000000UL,

SSI_FRF_MOTO_MODE_0,

SSI_MODE_SLAVE,

1000000,

16);

SSIIntClear(SSI0_BASE, SSI_RXFF);

SSIIntEnable(SSI0_BASE, SSI_RXFF);

IntPrioritySet(INT_SSI0, 0xE0);

IntEnable(INT_SSI0);

SSIEnable(SSI0_BASE);

}

void SSI0_Handler()

{

uint32_t temp;

SSIIntClear(SSI0_BASE, SSI_RXFF);

while(SSIDataGetNonBlocking(SSI0_BASE, &temp))

{

spiData[i_wr] = temp;

if(++i_wr >= N_RAW_BUF)

i_wr = 0;

}

}