Other Parts Discussed in Thread: TL081, LM741

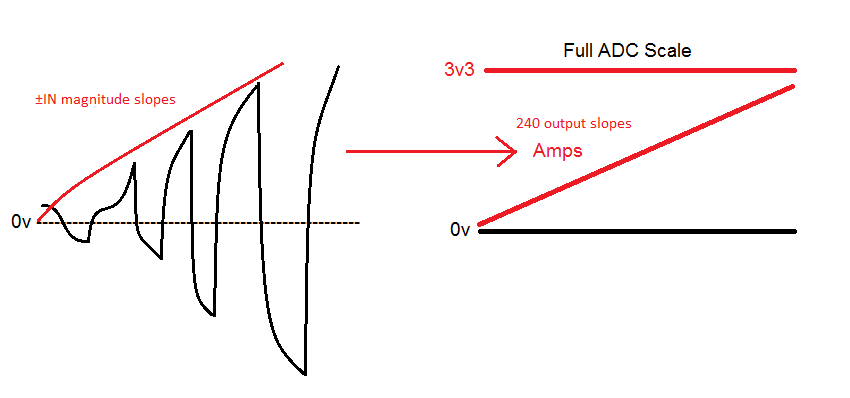

Single ended analog input signal 1.65v threshold has poor digital granularity for magnitude changes > +/-100mV relative mid VREFP.

How can ADC single ended sensitivity be improved so even +/-50mV steps increase or decrease register values >100mV relative mid VREP?

All magnitude changes >100mV flat line near mid supply and scaling by 4096 is mostly NULL. Otherwise not from 0v up to 1.65v or even up to VREFP 3v3 on single ended inputs.

Seemingly we need to make 1.65v produce 0x0 register integers where each 50mv = 0x3E8 or +/-1000 relative to ADC scale factor 4096. This seems impossible to achieve from any single ended input. Yet other TI forum claim an OPAMP output to any single ended ADC input channel produces correct digital translation from mid VREFP. That claim seems misleading as it can not be achieved with any granular results >100mV and makes OPAMP appear to have very bad precision. Why some TI people make it so complicated and obviously mislead others in the process is baffling or even intentional.

ADC single ended input seemingly has no way to process a bipolar signal from 1/2 VREFP with any kind of refined granularity, e.g. >100mV relative mid VREFP. Please enlighten us all how it can be done with examples of working software or ADC configurations for single ended inputs. Seemingly double ended ADC inputs must be combined for the single ended OPAMP signal produce correct results from mid VREFP with >100mV granularity in either direction.