Hi e2e,

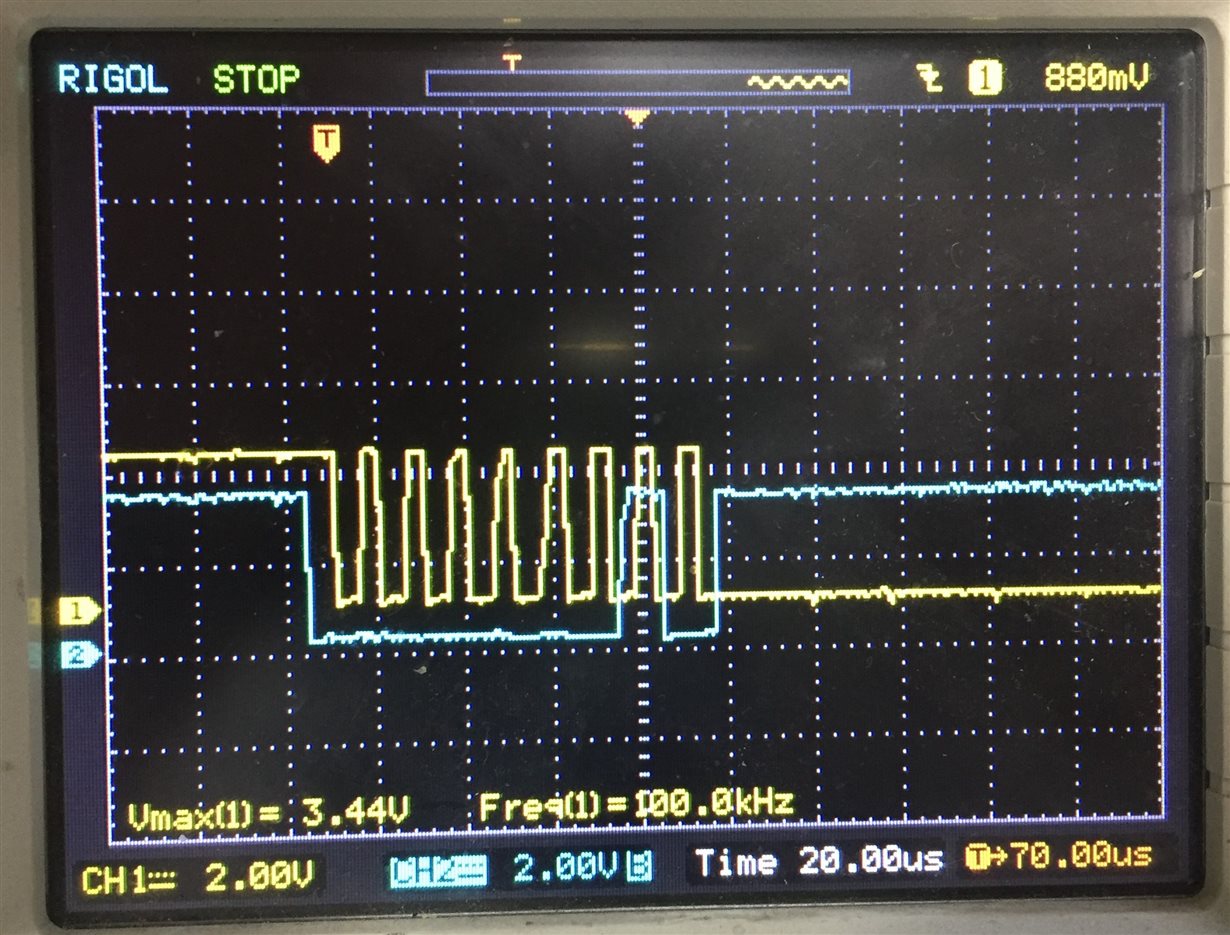

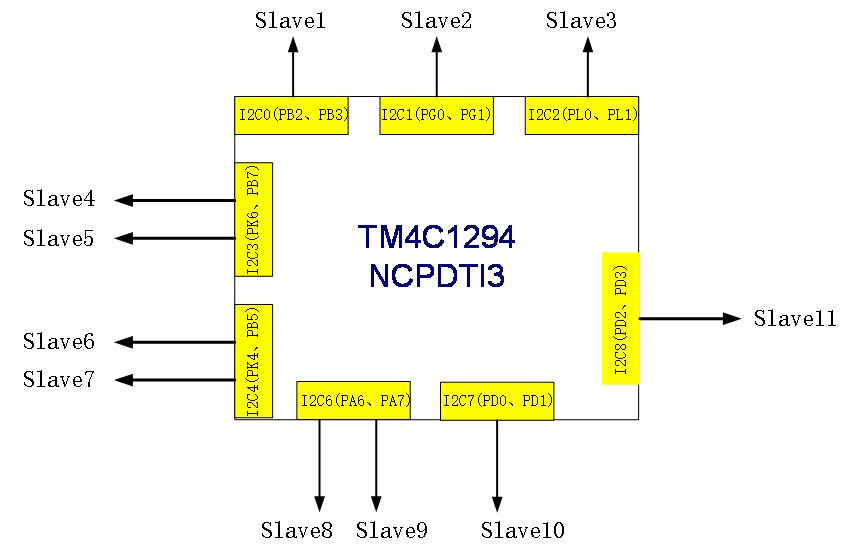

Here we have a customer using TM4C1294 I2C as master, the slave are sensors and other MCU, they meet a problem that the SCL will pull low and the 9th SCL is not sent out, below shows the register while error coming out.

We are very confused that why the 9th SCL is not sending out, what's the status of this condition, need your help, thanks in advance.