Other Parts Discussed in Thread: EK-TM4C1294XL, EK-TM4C123GXL

From my customer:

We are using some TM4C129 Tiva microcontrollers on a couple of our products. We recently discovered an issue with the Tiva’s I2C bus’s SDA signals glitching low when the chips are reset. Can you help us figure out if this is expected behavior or not, and if we need to change our I2C configuration to safely handle chip resets?

We currently configure the SDA pins with the following calls into the TivaWare API:

GPIOPinConfigure(GPIO_PB3_I2C0SDA);

GPIOPinTypeI2C(GPIO_PORTB_BASE, GPIO_PIN_3);

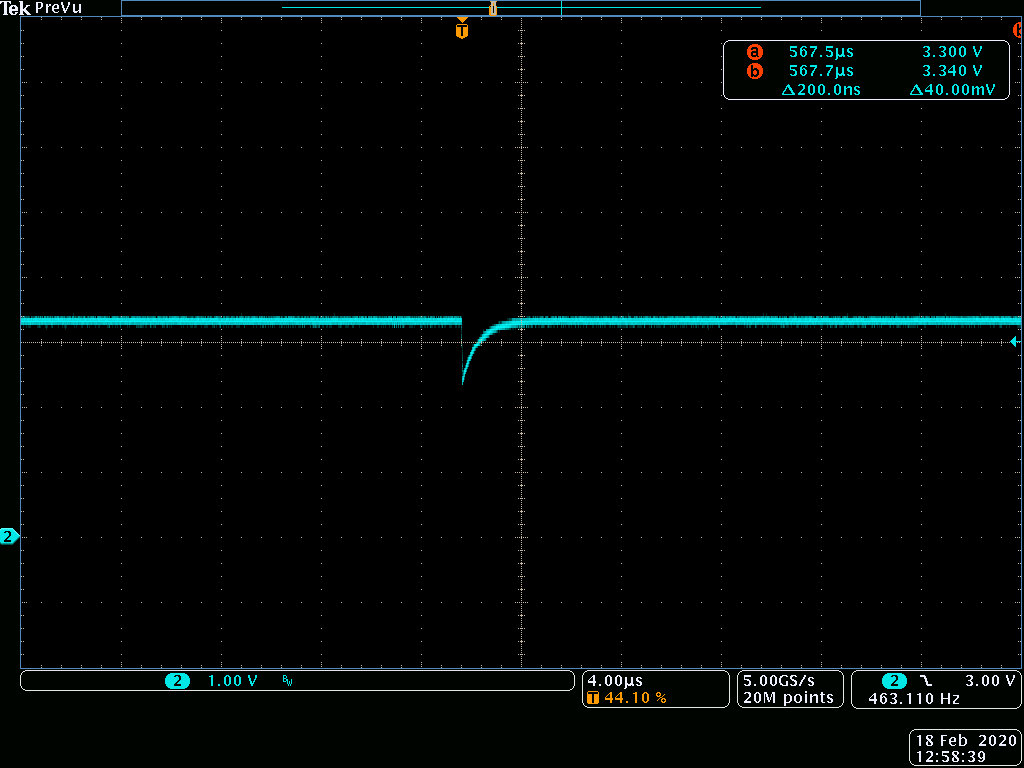

Later, our firmware issues two different types of reset – Software System Reset (by calling SysCtlReset()) and Watchdog Timer Reset (by allowing the watchdog timer to expire). Upon reset, the SDA signal is driven low momentarily and then released, as seen in the attached screenshot (oscilloscope channel 4).

We have played around with various register configurations prior to issuing the resets, and we found that calling GPIOPadConfigSet(GPIO_PORTB_BASE, GPIO_PIN_3, GPIO_STRENGTH_2MA,GPIO_PIN_TYPE_ANALOG) right before issuing a reset seems to resolve the issue. We don’t know why these register settings resolve the issue, so we’re hesitant to implement this particular fix without your consent that it is an acceptable and repeatable fix. Can you advise us?