Other Parts Discussed in Thread: EK-TM4C1294XL, TM4C1294NCPDT

Hello,

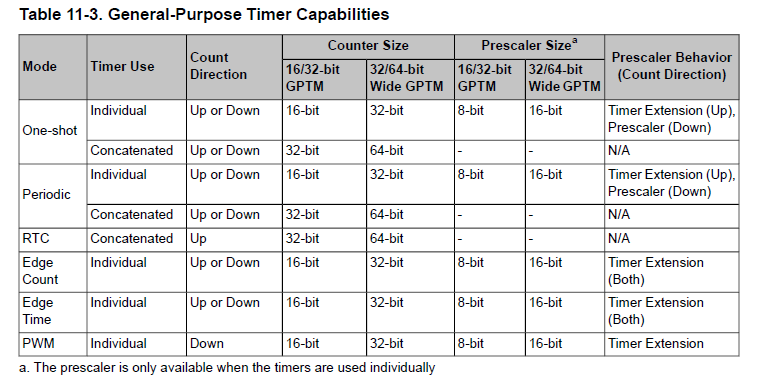

here is my code to configure timer0A as a capture compare PWM it works with only 16 bit operating modes, I just want to configure it with 32 bit operating mode:

void init_timer(void)

{

// Enable and configure Timer0 peripheral.

SysCtlPeripheralEnable(SYSCTL_PERIPH_TIMER0);

// Initialize timer A and B to count up in edge time mode

TimerConfigure(TIMER0_BASE, (TIMER_CFG_SPLIT_PAIR | TIMER_CFG_A_CAP_TIME));//when i'm trying to change TIMER_CFG_SPLIT_PAIR it doesn't work

// Timer a records pos edge time

TimerControlEvent(TIMER0_BASE, TIMER_A, TIMER_EVENT_POS_EDGE);

//configure timer to count all its width

TimerLoadSet(TIMER0_BASE, TIMER_A, 0xFFFF);//so when i putting(0xFFFFFFFF)it just loads (0xFFFF)

//Configure the pin that the timer reads from (PB6)

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOB);

GPIOPinConfigure(GPIO_PB6_T0CCP0);

GPIOPinTypeTimer(GPIO_PORTB_BASE, GPIO_PIN_6);

// Registers a interrupt function to be called when timer b hits a neg edge event

IntRegister(INT_TIMER0A, ISR_Capture);//ISR_Capture is my ISR code

// Makes sure the interrupt is cleared

TimerIntClear(TIMER0_BASE, TIMER_CAPA_EVENT);

// Enable the indicated timer interrupt source.

TimerIntEnable(TIMER0_BASE, TIMER_CAPA_EVENT);

// The specified interrupt is enabled in the interrupt controller.

IntEnable(INT_TIMER0A);

}

So, what should i do or change to make the timer works with 32 bit as a capture compare unit?