Other Parts Discussed in Thread: HALCOGEN

Tool/software: Code Composer Studio

Dear team

The device is RM42L432.

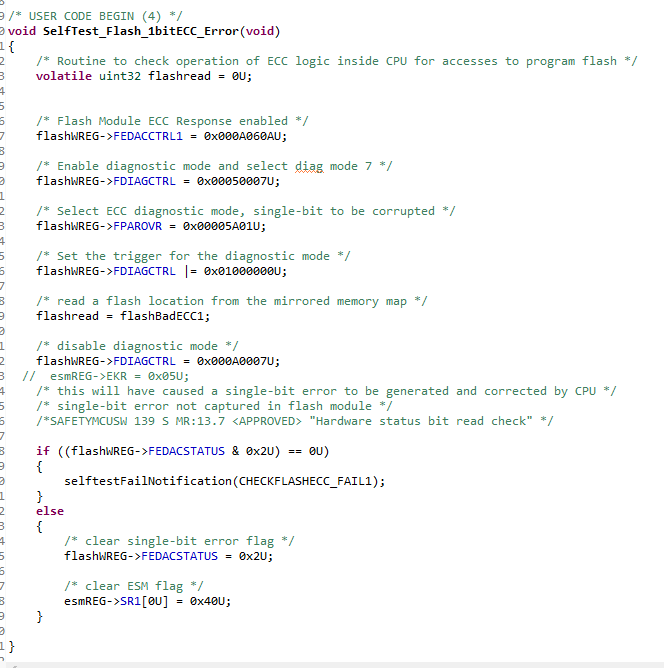

1 Problems were found when i used SL_SelfTest_Flash.

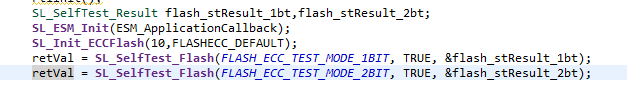

flash_stResult_1bt was ST_PASS when running retVal = SL_SelfTest_Flash(FLASH_ECC_TEST_MODE_1BIT, TRUE, &flash_stResult_1bt);

But flash_stResult_2bt was ST_FAIL; when running retVal = SL_SelfTest_Flash(FLASH_ECC_TEST_MODE_2BIT, TRUE, &flash_stResult_2bt);

What may cause the difference?

2 Besides,I enabled interrupt trigger and nerror pin in FLASH_ECC_TEST_MODE_1BIT mode in HALcogen.

However, it does not trigger an interrupt and pull the pin low during operation.

BR,

SUSAN